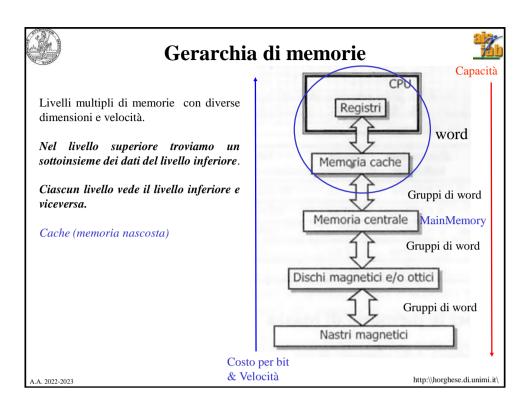

## La struttura delle memorie cache

Prof. Alberto Borghese Dipartimento di Informatica

alberto.borghese@unimi.it

Università degli Studi di Milano

Riferimento Patterson: 5.2, 5.4, 5.9, B.9

A.A. 2022-2023 1/52 http:\\horghese.di.unimi.it\

# Sommario

$http: \hspace{-0.05cm} \hspace{-$

Memory miss

**SRAM**

**DRAM**

Trasferimento dati

### Gestione dei fallimenti di una cache

La gestione avviene tra CPU e MMU.

latenza.

Hit – è quello che vorremmo ottenere, il funzionamento della CPU non viene alterato.

Miss – in lettura devo aspettare che il dato sia stato caricato nella linea di cache e sia pronto

-> eccezione particolare della CPU che crea uno stallo della CPU e non un flush.

Nelle CPU super-scalari si sfrutta l'esecuzione fuori ordine per nascondere questa

#### Passi da eseguire in caso di Miss (miss penalty):

- Bloccare tutte le istruzioni nella pipeline (blocco dei registri di pipeline per uno o più cicli di clock)

- 2) Scaricare in MM la linea di cache interessata (micro-blocco).

- 3) Richiedere che la MM legga il micro-blocco contenente il dato da leggere e lo porti fuori nel MDR.

- 4) Trasferire il micro-blocco in cache, aggiornare i campi validita'e tag.

- 5) Riavviare l'esecuzione della pipeline.

NB Il programma non può continuare!!

A 2022 2023 4/52

$http: \hspace{-0.05cm} \hspace{-$

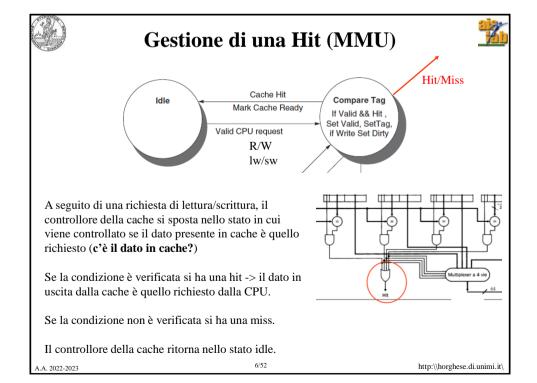

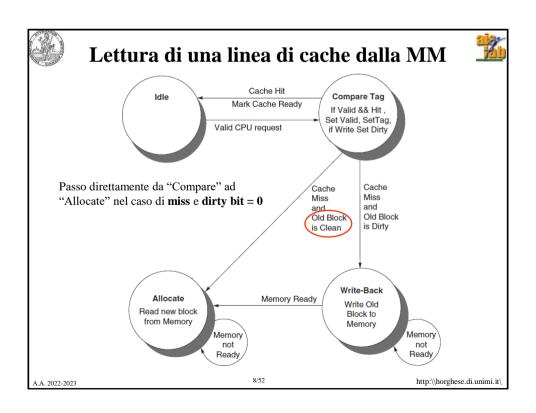

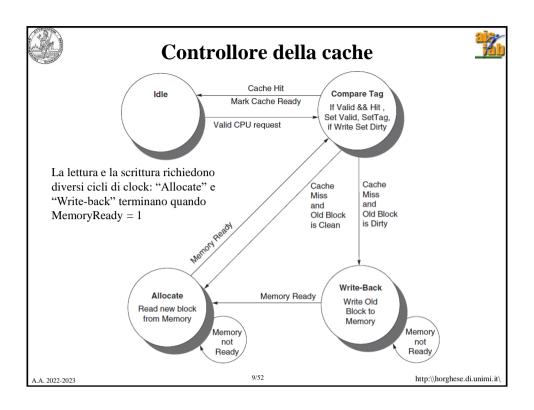

## Controllo mediante FSM nella MMU

Stato = situazione

#### STATI del controllore (S):

- "Idle": non ci sono richieste alla cache

- "Compare": identificazione di Hit / Miss

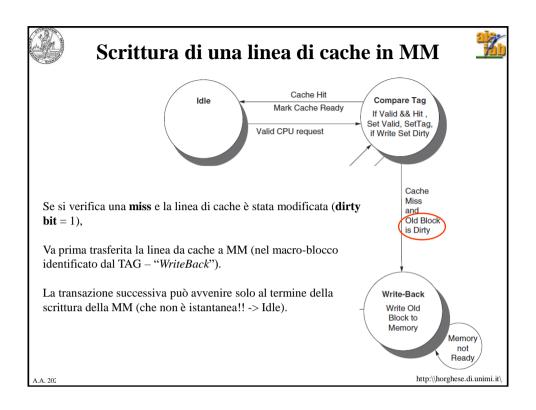

- Scrittura della linea di cache in MM

- Lettura della linea di cache dalla MM

Meccanismo per decidere se una linea va scaricata: dirty bit = 1 se la linea è stata modificata dalla CPU

(bit di validità + dirty bit).

#### INPUT al controllore (I):

- Read/Write MM

- DirtyBit linea cache

- MM Ready

#### **OUTPUT** del controllore (Y):

Hit/miss (il dato presente in uscita è quello richiesto dalla CPU).

A.A. 2022-2023

<S, I, Y, f(S,I), g(S), S<sub>0</sub>>

MMU

A. 2022-2023

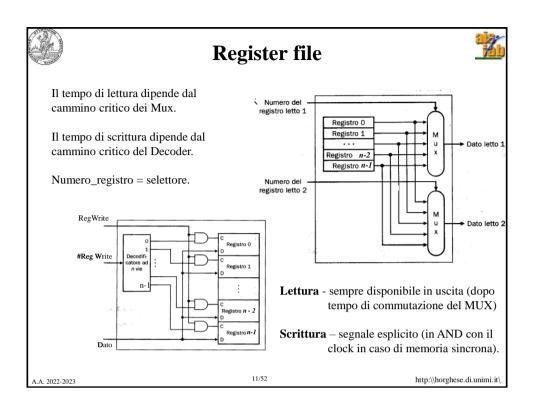

# SRAM oggi

http:\\horghese.di.unimi.it\

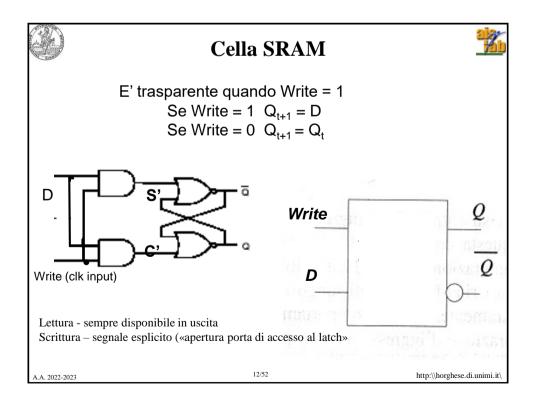

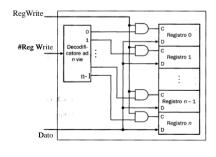

Static RAM. Bistabili (4-6 **transistor** per cella, ottimizzazione della cella rispetto al latch, cf. Register File).

Tempo di accesso uguale per ogni dato.

Informazione stabile (non ci sono disturbi da parte di quello che succede intorno)

Non c'è bisogno di rinfrescare il contenuto della memoria (refresh)

Sono memorie volatili (dipendono dall'alimentazione)

Con la tecnologia CMOS, consumano energia solo quando commutano. Poca energia viene consumata per mantenere il dato (**standby**).

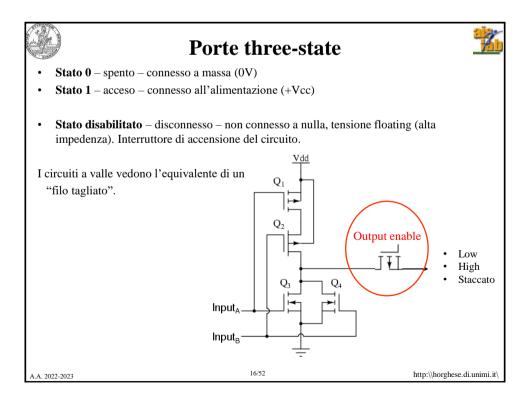

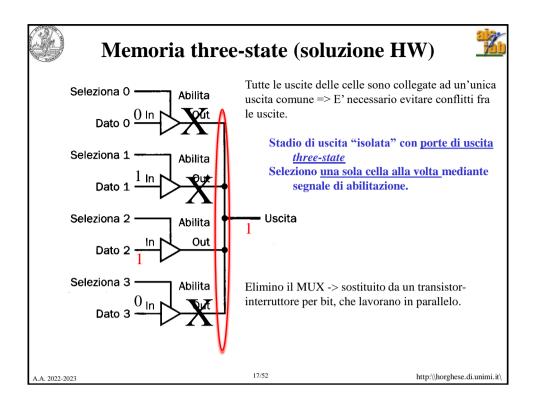

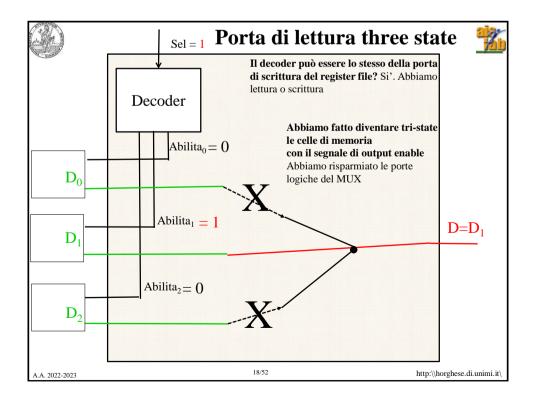

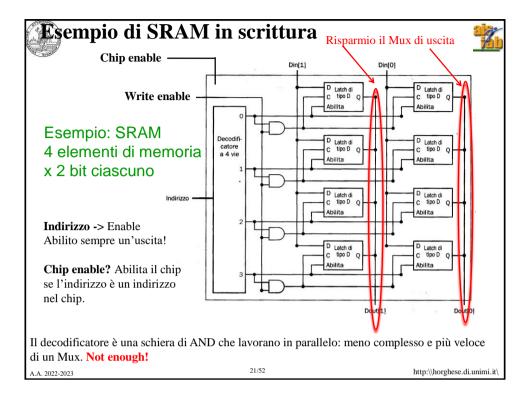

# SRAM - 1 sola porta di lettura / scrittura (o leggo o scrivo o non faccio nulla: 2 segnali)

Cache -> inserita nella CPU -> Produzione delle SRAM è principalmente da parte dei produttori di CPU.

Memorie veloci per dispositivi embedded.

A.A. 2022-2023 13/52 http:\\horghese.di.unimi.it\

14/52

## **SRAM**

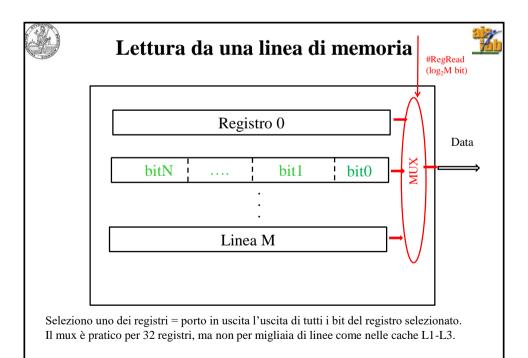

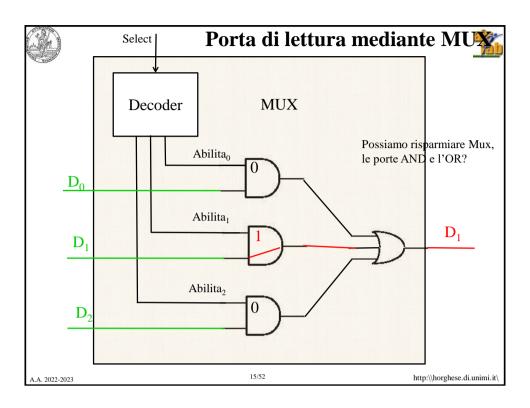

- Visione logica

- struttura rettangolare o lineare

- Indirizzo come {numero di linea, numero di colonna} o numero di elemento

- Visione fisica

- La memoria è costituita da chip

- Struttura rettangolare o lineare

Indirizzo della linea

- Come costruiamo una memoria logica con i chip di memoria?

19/52 http:\\horghese.di.unimi.it\ A.A. 2022-2023

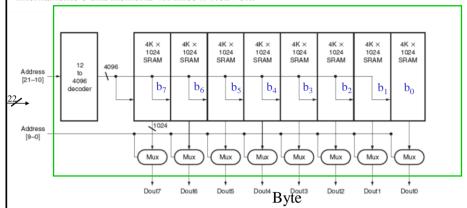

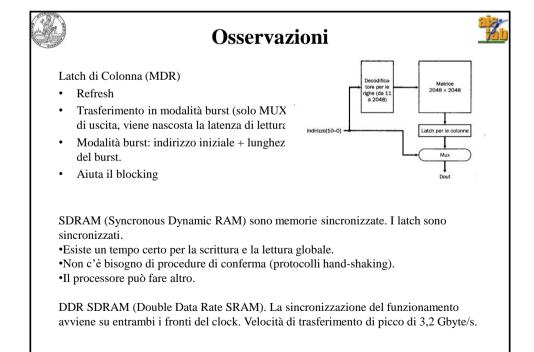

### **SRAM** a matrice

Una **SRAM 4M x 8** avrebbe bisogno di un decoder a 22 bit -> 4M linee, con 4M porte AND ciascuna con 22 bit in ingresso.

C'e' un limite elettrico al numero di linee che si possono collegare assieme e aumenta il tempo di commutazione.

$E'\ più\ conveniente\ costruire\ una\ matrice\ e\ separare\ la\ lettura\ delle\ linee\ dalla\ lettura\ delle\ colonne\ (estrazione\ di\ una\ linea\ «lunga»\ dalla\ memoria\ - cf.\ Memoria\ cache).$

## **SRAM** a matrice

**SRAM 4M x 8**. Ad ogni bit assegno un chip (banco) di 4K linee x 1024 bit per linea (4M bit => internamente è una memoria 4K linee x 1.024 bit.

Il decodificatore sarà a 12 bit ( $\log_2 4K$ ) per selezionare una delle 4096 linee (ciascuna di 1024 bit). Ciascuna linea fornisce 1024 bit.

La stessa linea sarà selezionata in ogni banco di memoria  $\Rightarrow$  porto fuori 1.024 x 8 = 8 Kbyte. Seleziono 1 bit da ogni banco con il Mux (controllato dai 10 bit meno significativi,  $\log_2 1.024$ ). => Ottengo 1 x 8 = 1 Byte.

Nell'approccio non a matrice avrei avuto bisogno di un decodificatore a 22 bit (log<sub>2</sub>4M).

it\

Leggo prima una intera linea e poi attraverso i mux di uscita leggo 1 parola alla volta (1 Byte) Lettura gerarchica in 2 passi.

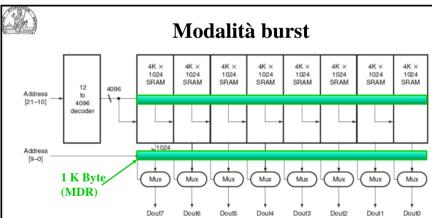

#### Syncronous Static RAM (SSRAM) -> trasferisco burst.

**Burst:** indirizzo iniziale (e.g. indirizzo del primo elemento di un vettore) + lunghezza del burst (numero byte consecutivi. In questo caso al massimo saranno 1K elementi pari alla lunghezza della linea di uscita).

- Non viene richiesto di specificare un nuovo indirizzo per ogni byte -> sono adiacenti.

- E' una tecnica potente per portare fuori da una SRAM e leggere blocchi di memoria.

.A. 2022-2023 24/52 http:\\horghese.di.unimi.it\

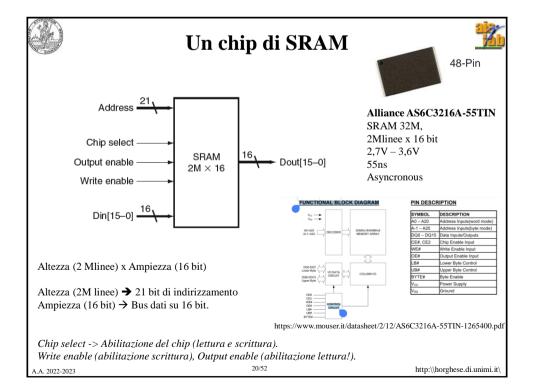

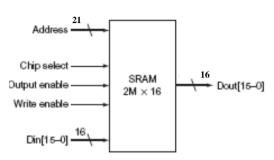

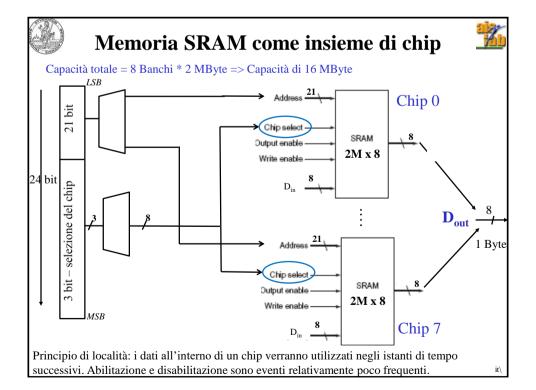

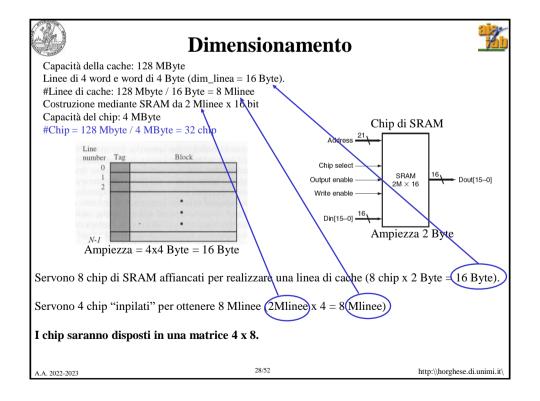

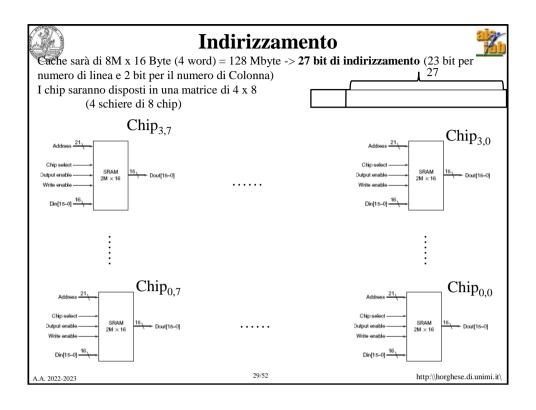

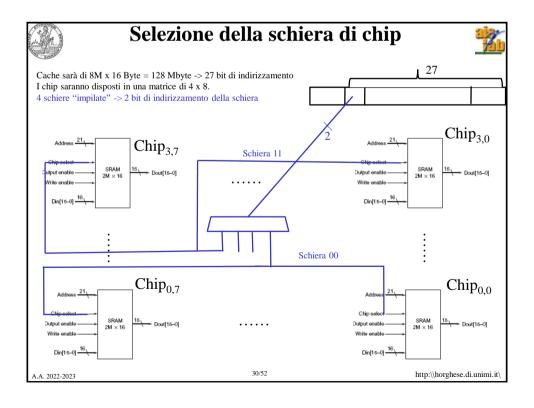

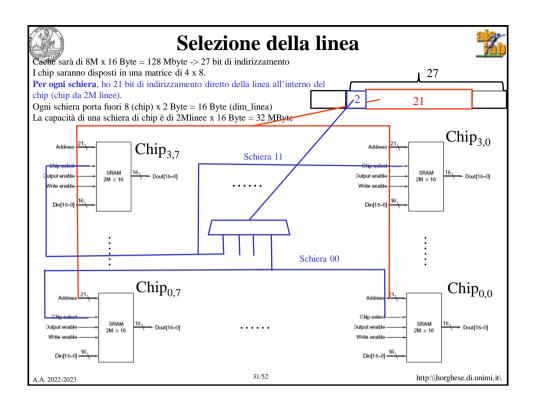

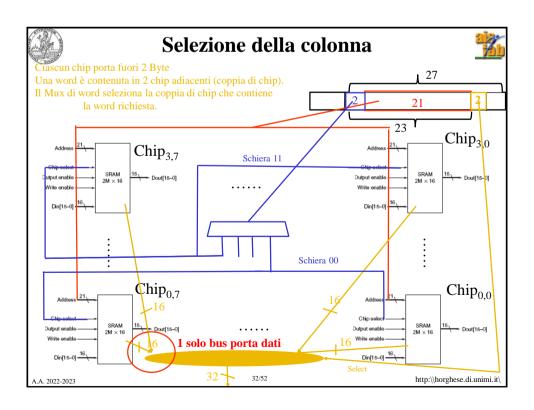

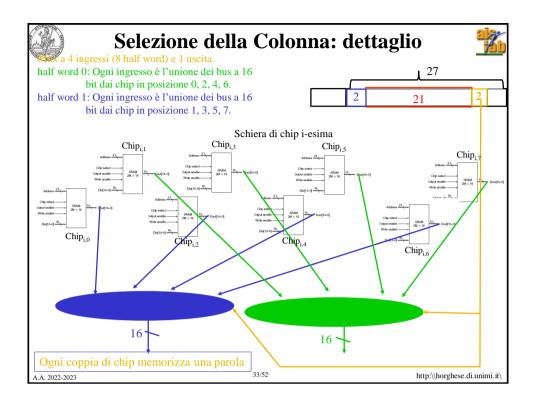

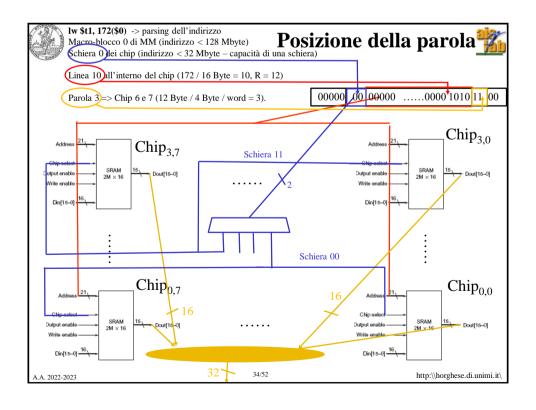

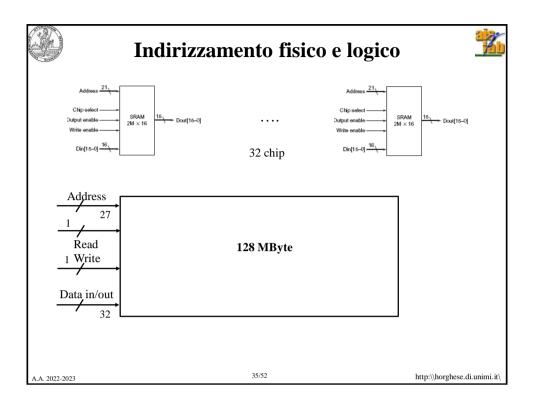

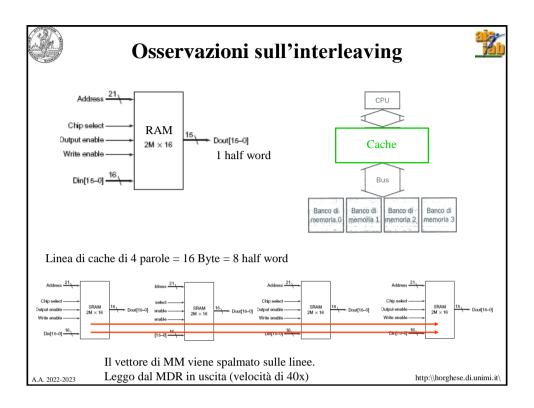

# Chip di SRAM (2M x 16)

Tempo di accesso: da Address a Dout.

Altezza (2 Mbit) x Ampiezza (16 bit) - Oggi 1-4 bit

Altezza (2 Mbit) → 21 bit di indirizzamento Ampiezza (16 bit) → Bus dati su 16 bit.

Chip select -> Abilitazione del chip (per risparmiare energia, indirizzo nel range del chip).

Write enable (abilitazione scrittura), Output enable (abilitazione lettura!).

A.A. 2022-2023 25/52 http://horghese.di.unimi.it/

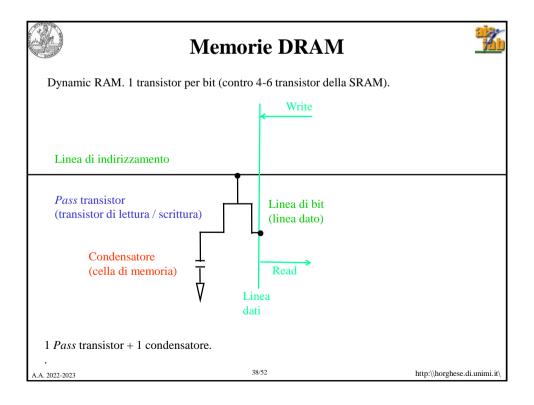

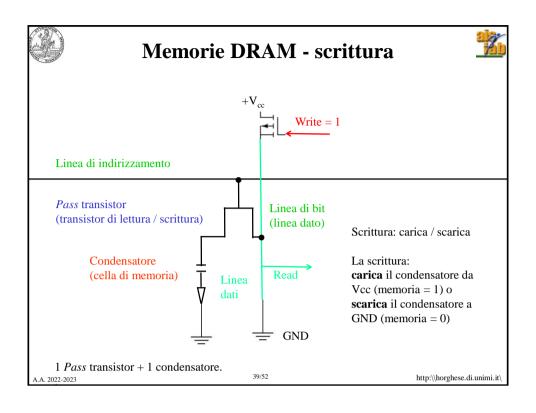

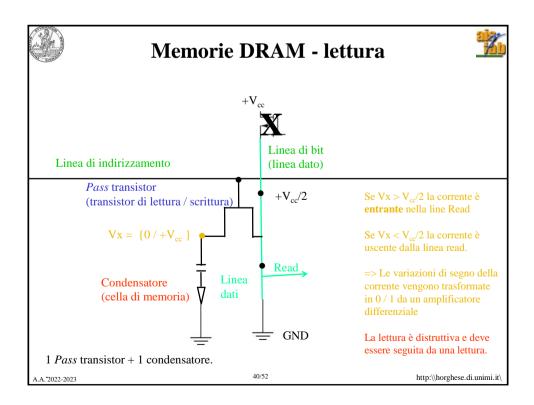

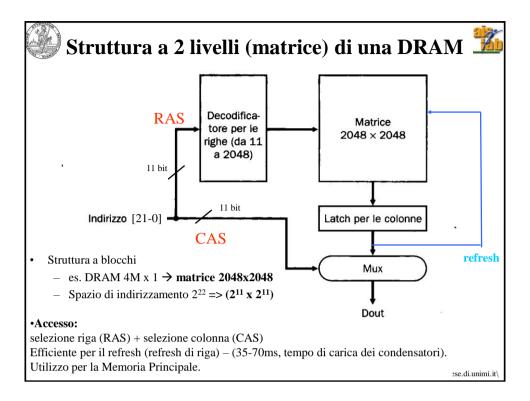

# I problemi delle DRAM

I condensatori sono componenti passivi -> richiedono tempo per caricarsi e scaricarsi.

La lettura è distruttiva.

I condensatori .... si scaricano (qualche millisecondo)

Refresh gestito autonomamente dal controllore della memoria mediante ciclo lettura/scrittura

Cosa leggo/scrivo? Quale/i bit?

.A. 2022-2023 42/52

$http: \hspace{-0.5em} \hspace{-0.5em$

44/52

http:\\horghese.di.unimi.it\

A. 2022-2023

# Specifiche delle DRAM

| Anno<br>introduzione | Dimensione chip | \$ per GiB  | Tempo accesso<br>totale a nuova<br>riga / colonna | Tempo medio<br>di accesso alla<br>riga esistente |

|----------------------|-----------------|-------------|---------------------------------------------------|--------------------------------------------------|

| 1980                 | 64 Kibibit      | \$1 500 000 | 250 ns                                            | 150 ns                                           |

| 1983                 | 256 Kibibit     | \$ 500 000  | 185 ns                                            | 100 ns                                           |

| 1985                 | 1 Mebibit       | \$ 200 000  | 135 ns                                            | 40 ns                                            |

| 1989                 | 4 Mebibit       | \$ 50 000   | 110 ns                                            | 40 ns                                            |

| 1992                 | 16 Mebibit      | \$15000     | 90 ns                                             | 30 ns                                            |

| 1996                 | 64 Mebibit      | \$10000     | 60 ns                                             | 12 ns                                            |

| 1998                 | 128 Mebibit     | \$ 4000     | 60 ns                                             | 10 ns                                            |

| 2000                 | 256 Mebibit     | \$ 1000     | 55 ns                                             | 7 ns                                             |

| 2004                 | 512 Mebibit     | \$ 250      | 50 ns                                             | 5 ns                                             |

| 2007                 | 1 Gibibit       | \$ 50       | 45 ns                                             | 1,25 ns                                          |

| 2010                 | 2 Gibibit       | \$ 30       | 40 ns                                             | 1 ns                                             |

| 2012                 | 4 Gibibit       | \$ 1        | 35 ns                                             | 0,8 ns                                           |

| 2015                 | 8 Gibibit       | \$7         | 30 ns                                             | 0,6 ns                                           |

| 2018                 | 16 Gibibit      | \$6         | 25 ns                                             | 0,4 ns                                           |

|                      |                 |             |                                                   |                                                  |

Tempo totale di accesso (dall'arrivo dell'indirizzo al dato in uscita): 25 ns Tempo di accesso in modalità burst (accesso al buffer di linea di uscita): 0.4 ns

60 volte più veloce!

45/52

http://horghese.di.unimi.it

# Organizzazione della memoria

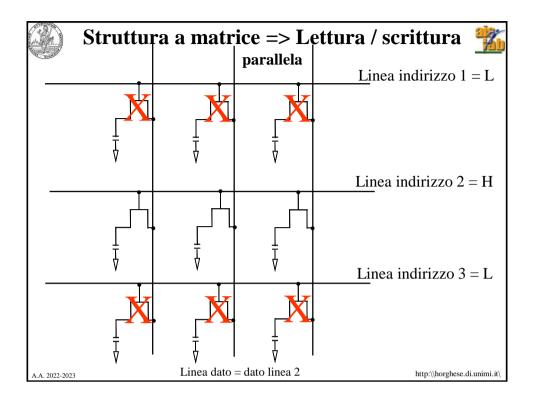

Organizzazione a matrice (cf. cache) Organizzazione gerarchica.

A.A. 2022-2023 46/52 http:\\horghese.di.unimi.it\

## **Sommario**

Memory miss

**SRAM**

**DRAM**

Trasferimento dati

A.A. 2022-2023 47/52

## Gestione dei fallimenti di una cache

http:\\horghese.di.unimi.it\

http:\\horghese.di.unimi.it\

La gestione avviene tra CPU e MMU.

Hit – è quello che vorremmo ottenere, il funzionamento della CPU non viene alterato.

Miss – in lettura devo aspettare che il dato sia stato caricato nella linea di cache e sia pronto

-> eccezione particolare della CPU che crea uno stallo della CPU e non un flush.

Nelle CPU super-scalari si sfrutta l'esecuzione fuori ordine per nascondere questa latenza.

#### Passi da eseguire in caso di Miss (miss penalty):

- Bloccare tutte le istruzioni nella pipeline (blocco dei registri di pipeline per uno o più cicli di clock)

- 2) Scaricare in MM la linea di cache interessata (micro-blocco).

- 3) Richiedere che la MM legga il micro-blocco contenente il dato da leggere e lo porti fuori nel MDR.

- 4) Trasferire il micro-blocco in cache, aggiornare i campi validita'e tag.

- 5) Riavviare l'esecuzione della pipeline.

NB Il programma non può continuare!!

A 2022 2022 48/52

## I componenti della Miss penalty

Tempi di accesso:

1 ciclo di clock per inviare l'indirizzo.

15 cicli di clock per ciascuna attivazione della Memoria Principale (dall'invio dell'indirizzo alla parola in uscita)

1 ciclo di clock per trasferire una parola al livello superiore (cache).

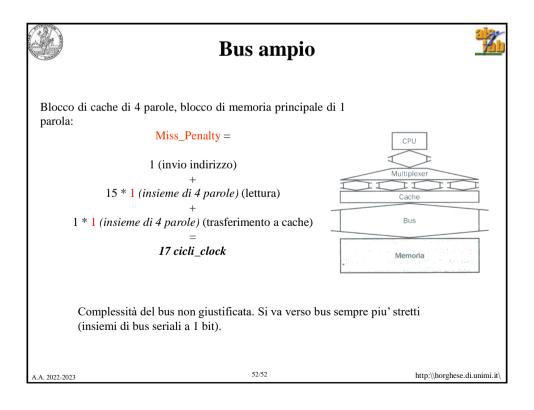

Blocco di cache di 4 parole, blocco di memoria principale di 1 parola:

Miss\_Penalty =

1 (invio indirizzo)

15 \* 4 (parole) (lettura)

1 \* 4 (parole) (trasferimento a cache)

65 cicli\_clock

#### **Obbiettivi:**

•Diminuire la penalità di fallimento (miss\_penalty).

49/52

M.COIO

A.A. 2022-2023

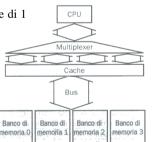

# **Interleaving**

Blocco di cache di 4 parole, blocco di memoria principale di 1 parola:

Miss\_Penalty =

1 (invio indirizzo)

(IIIVIO IIIGIIIZZO)

15\*1 (insieme di 4 parole) (lettura)

1 \* 4 (parole) (trasferimento a cache)

20 cicli\_clock

Interleaving (interallacciamento). Banchi che potrebbero essere trasferiti in parallelo alla cache. Si sposa perfettamente con la **struttura gerarchica** della memoria e con la **modalità di trasferimento a burst**.

\(\Lambda\). A. 2022-2023 50/52 http:\\horghese.di.unimi.it\)

# Sommario

Memory miss

SRAM

DRAM

Trasferimento dati

A.A. 2022-2023 53/52 http:\\horghese.di.unimi.it\