## Le virtual machine e la memoria virtuale

Prof. Alberto Borghese Dipartimento di Informatica

alberto.borghese@unimi.it

Università degli Studi di Milano

Riferimento Patterson: 5.6, 5.7, 2.12.

A.A. 2019-2020 1/53 http://borghese.di.unimi.it/

# Sommario

$http: \hspace{-0.05cm} \ \ \, | borghese.di.unimi.it \rangle$

#### Le virtual machine

La memoria virtuale

La traduzione degli indirizzi

## Virtual machines (VM)

La VM è un software che fornisce un **ambiente completo** a **livello di sistema**, compatibile con una certa ISA (e.g. MS-DOS): VMware, ESX Server...

Sviluppate negli anni 60 e riprese recentemente per:

- Sicurezza e isolamento di sotto-sistemi.

- Condivisione dello stesso sistema da parte di molti utenti (e.g. cloud computing)

- Riproduzione di SO vintage.

Velocità dei processori rende il costo della virtualizzazione accettabile.

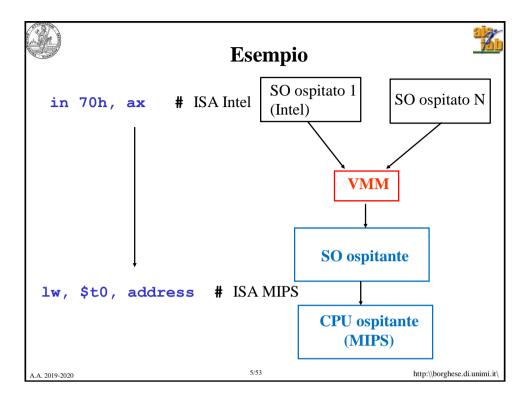

Lo stesso calcolatore può **supportare più VM** e può quindi supportare più SO e ambienti, anche obsoleti quali ad esempio il DOS e quindi programmi non più eseguibili direttamente. Esempio:

- MS-DOS

- Linux Ubuntu

- Beta-release di un SO (per testing)

Può consentire l'esecuzione di un'applicazione nel suo ambiente nativo (versione corretta del SO: e.g. Windows 7, Windows XP).

### Caratteristiche

SW di emulazione. (e.g. Java Virtual Machine): non è una macchina fisica!

VM di un'ISA: ambiente di sistema congruente con una certa ISA (elementi di stato, funzionalità messe a disposizione dall'HW).

Le VM creano l'illusione, ad esempio, di avere a disposizione una macchina MS-DOS su una macchina il cui SO è Linux.

Essendo SW, diverse VM possono essere eseguite sulla stessa macchina ospitante, emulando diversi SO. Vengono eseguite in modo segregato. Ciascuna macchina, quando è in esecuzione, utilizza l'hardware a disposizione come fosse suo.

Il software eseguito da una VM (software ospitato) deve essere eseguito esattamente come se fosse eseguito sull'ISA nativa (a parte le prestazioni).

.A. 2019-2020 4/53 http:\\borghese.di.unimi.it\

# Il Monitor (VMM)

Le VM sono supportate da uno strato software particolare chiamato **Monitor della Virtual Machine** (VMM) o **Hypervisor**. Questo software fa da tramite tra le diverse VM e l'ambiente ospitante (hardware + SO).

Il costo principale è legato all'intervento del SO dell'ospitante per tradurre le richieste al SO della VM (I/O, memoria....)

E' la parte di controllo della VM. E' un ruolo delicato:

- Deve proteggere i SW ed i sistemi operativi ospitati.

- Deve proteggersi dagli (altri) sistemi operativi ospitati.

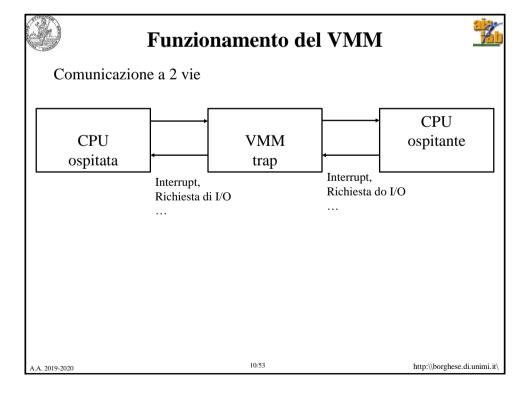

### Il funzionamento del VMM

#### Solitamente:

- un VMM ha privilegi di sistema (deve interfacciarssi con la CPU ospitante).

- una VM ha i privilegi di utente (è equivalente a un comune programma per la CPU ospitante).

Il software eseguito da una VM **non deve modificare nulla delle risorse della macchina ospitante, direttamente**, ma deve passare attraverso il SO della macchina ospitante.

Un VMM mappa le risorse virtuali (della VM) nelle risorse fisiche della CPU:

- Time-sharing

- Partizionamento

- Emulazione.

- Multi-thread.

Per **esempio**, nel caso in cui un processo ospitato (guest) sia basato su un timer (eccezione di sistema), l'eccezione dovrà essere simulata dal VMM. La simulazione potrebbe utilizzare il timer di sistema o meno a seconda che la CPU lo renda accessibile o meno.

Il timer del processo ospitato non accede direttamente al timer, ma ci accede attraverso il VMM che si interfaccia con il SO della macchina ospitante.

## Il VMM e le istruzioni privilegiate

Il costo della virtualizzazione dipende dal tipo di processo eseguito. Tanto **maggiore** è il ricorso al SO, tanto **maggiore** il costo della virtualizzazione (e.g. processi con un I/O intensive hanno un overhead elevato, processi di calcolo intensive hanno poco over-head).

### L'overhead dipende

- Numero di chiamate al SO (e di istruzioni che devono essere emulate)

- Aumento del tempo di esecuzione di ciascuna di queste istruzioni (e.g. timer emulato HW a un costo molto inferiore di un'emulazione SW).

### Richiesta al SO

Cosa succede quando un SO ospitato fa una richiesta privilegiata (e.g. lancia un interrupt o un'eccezione?).

Queste devono essere intercettate (**trap**) dal VMM che le gestirà nel modo più appropriato tenendo conto dello stato della CPU opsitante e delle altre VM.

Questo processo può rilevarsi molto costoso soprattutto quando l'applicazione ospitata fa molto uso di I/O ma anche di altre funzionalità.

Applicazioni che eseguono principalmente funzioni di calcolo o fanno poco utilizzo della virtualizzazione, sono quelle eseguite più velocemente dalle VM.

A.A. 2019-2020 9/53 http:\\borghese.di.unimi.it\

# **Amazon Web Services (AWS)**

### Utilizza le VM per il cloud computing:

- I diversi utenti vengono protetti uno dall'altro.

- Il SO e la sua configurazione richiesta da un cliente possono venire istallate su più machine del cloud.

- AWS può eliminare le VM che non servono più risparmiando risorse.

- Si possono utilizzare macchine eterogenee, non della stessa generazione, aggiornandole via via. Le prestazioni vengono specificate "Equivalent CPU capcity".

- Il VMM può essere configurato per misurare:

- Lo spazio su disco

- L'utilizzo della rete

- L'utilizzo del processore

Per poi fatturare al cliente.

A.A. 2019-2020 11/53 http:\\borghese.di.unimi.it\

# Sommario

http:\\borghese.di.unimi.it\

Le virtual machine

La memoria virtuale

La traduzione degli indirizzi

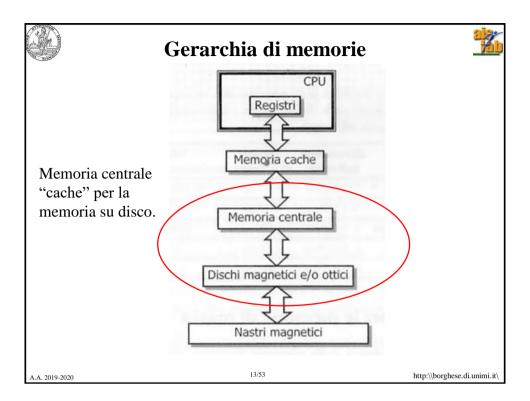

# Le origini della Memoria Virtuale

1) L'insieme di dati e di memoria (**working set**) di un task può essere maggiore di quanto si può caricare in memoria principale.

Il working set si può suddividere in moduli che possono risiedere alternativamente in memoria. Questi moduli condividono lo stesso spazio di indirizzi fisico e non potranno coesistere nella memoria.

Il meccanismo che gestisce il caricamento / scaricamento dei moduli di uno stesso task si chiama(va) **overlay**. Era il programmatore a specificare quali moduli potevano essere in overlay, poi ha iniziato a pensarci il linker. **Moduli bilanciati.**

2) Necessità di protezione dello spazio di memoria (principale) di un processo. Nessun altro processo deve potere scrivere nel suo spazio di lavoro (**protezione della memoria**).

### La memoria virtuale

Principio: distinzione tra memoria logica e memoria fisica.

Meccanismo. Viene assegnata la memoria principale logica a ogni processo in una quantità sufficientemente grande (anche maggiore della memoria fisica presente sulla CPU).

La memoria principale fisica è la stessa per diversi programmi in esecuzione, i quali condividono lo stesso spazio di indirizzamento fisico.

I programmi sono inizialmente residenti su disco.

La memoria virtuale consente di mappare lo spazio di memoria logico (software) di ciascun processo sulla memoria fisica (reale).

Lo spazio virtuale viene mappato dalla MMU sulla memoria principale fisica, evitando sovrapposizioni e consente una gestione sicura della memoria.

La memoria virtuale consente anche di nascondere al programmatore la **dimensione limitata della memoria principale fisica** rispetto alla memoria logica richiesta dal processo.

A.A. 2019-2020 15/53 http:\\borghese.di.unimi.it\

# Terminologia

Un blocco di memoria principale: virtuale o fisica (della stessa dimensione) viene chiamato **pagina** (equivalente alla linea della cache).

L'accesso alla memoria principale avviene mediante l'indirizzo virtuale (che è quello contenuto nel software, lw \$t0, address. Address fa quindi riferimento alla memoria virtuale – indirizzo virtuale).

L'indirizzo virtuale del processo deve essere trasformato in un indirizzo fisico dalla MMU.

- Il processo può essere mappato ovunque in MM.

- L'indirizzo fisico viene assegnato all'atto del caricamento (loading) del processo da disco a MM, viene caricato in un certo numero di pagine della memoria fisica.

Una miss dalla memoria principale in giù viene chiamata page fault.

Se si verifica una hit nella memoria principale, il micro-blocco viene trasferito dalla memoria principale alla linea di cache, se si verifica un page fault, occorre caricare la pagina da disco in memoria principale e poi trasferire il micro-blocco.

A.A. 2019-2020 16/53 http:\\borghese.di.unimi.it\

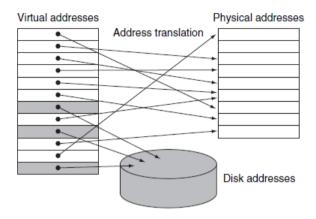

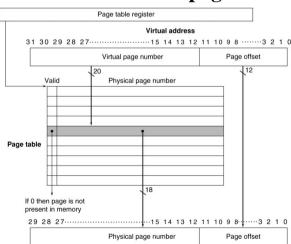

## Indirizzi fisici e indirizzi virtuali

Tabella delle pagine (mappatura)

Ciascun programma ha il suo spazio di indirizzamento (virtuale) che viene mappato su disco e sulla memoria principale (indirizzi fisici).

Il processore genera indirizzi virtuali mentre alla memoria si accede mediante indirizzi fisici.

### Indirizzamento della MM

Indirizzamento della MM: indirizzo base (indirizzo della pagina) + offset di pagina

# 31 30 29 28 27 ...... 15 14 13 12 11 10 9 8 ..... 3 2 1 0 Virtual page number Page offset Translation 29 28 27 ...... 15 14 13 12 11 10 9 8 .... 3 2 1 0

Virtual address

#### Physical address

Page offset

Altro esempio di base (numero di pagina) + offset

Il numero di pagine fisico è determinato dalla quantità di memoria fisica.

Physical page number

Il numero di pagine virtuali è virtualmente infinito: dipende dal numero di bit degli indirizzi virtuali. In questo caso 30 bit di indirizzamento della memoria fisica -> 1 Gbyte di memoria fisica e 32 bit di indirizzamento della memoria virtuale -> 4 Gbyte di memoria

# Criteri di progettazione della memoria virtuale

Strategie diverse da quelle utilizzate nelle cache. Obbiettivo principale è nascondere la penalità di page fault.

| Memory technology          | Typical access time     | \$ per GiB in 2012 |

|----------------------------|-------------------------|--------------------|

| SRAM semiconductor memory  | 0.5–2.5 ns              | \$500-\$1000       |

| DRAM semiconductor memory  | 50–70 ns                | \$10-\$20          |

| Flash semiconductor memory | 5,000-50,000 ns         | \$0.75-\$1.00      |

| Magnetic disk              | 5,000,000-20,000,000 ns | \$0.05-\$0.10      |

L'accesso a disco (magnetico) può essere quasi un milione di volte più lento della MM. 100 volte più lento nel caso ottimale di disco (a stato solido).

NB Questa penalità è dovuta largamente al tempo per accedere alla prima parola della pagina (latenza). Con il trasferimento a burst il resto dei dati viene trasferito più velocemente.

Occorre nascondere questa latenza! E minimizzare i page fault.

A.A. 2019-2020 19/53 http:\\borghese.di.unimi.it\

# Criteri di organizzazione della memoria principale

Le pagine devono essere sufficientemente ampie per ammortizzare i tempi di accesso (anche a seguito di una hit). Pagine di 4 KByte sono tipiche.

- Server -> 32/64 Kbyte

- Sistemi embedded -> 1 KByte

La mappatura delle pagine virtuali da disco sulla memoria principale è **completamente associativa** per massimizzare il riempimento della MM fisica ed evitare i page fault => Non c'è necessariamente contiguità tra le diverse pagine di uno stesso processo all'interno della MM fisica.

La gestione dei page fault può essere software (SO) visto il lungo tempo a disposizione per gestirli. Ottimizzazione del posizionamento delle pagine (scelta oculata di quale pagine scaricare su disco per fare posto a una nuova pagina).

La scrittura su disco di una pagina viene gestita in modalità write-back (con write buffer).

A.A. 2019-2020 20/53 http://borghese.di.unimi.it/

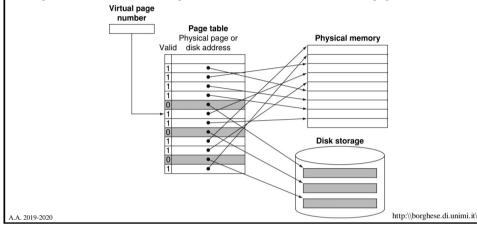

# Posizionamento delle pagine

Si utilizza la **Tabella delle pagine**, a sua volta residente nella memoria principale, indirizzata dal *registro della tabella delle pagine*.

Non si può cercare una pagina virtuale, controllando tutte le pagine contenute nella memoria fisica. Non si può utilizzare una tabella delle pagine associativa.

La tabella delle pagine è **indicizzata** con il numero della pagina virtuale (è una memoria ad accesso diretto).

La tabella delle pagine contiene la traduzione del numero di pagina virtuale in numero di pagina fisica. Controlla anche se la pagina fisica sia già presente nella memoria fisica (hit o miss).

#### Tabella delle traduzioni o mappatura. Ogni processo ha la sua PT.

E.g. Catalogo di una libreria (mappatura tra numero sequenziale del libro – indirizzo virtuale; e posizione nella libreria – indirizzo fisico). Alcuni libri possono non essere contenuti nella libreria locale ma in una libreria più grande (il disco).

A.A. 2019-2020 21/53 http:\\borghese.di.unimi.it\

# Tabella delle pagine

Physical address

L'altezza della memoria è teoricamente pari al numero di pagine virtuali. Per ogni pagina virtuale è riportata la traduzione. Bit di validità come nelle cache.

A.A. 2019-2020 22/53 http:\\borghese.di.unimi.it\

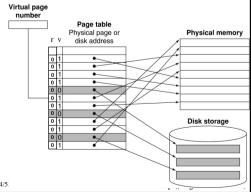

## Gestione di un page fault - I

All'avviamento di un processo il SO crea tutte le pagine del processo su disco (swap space). La pagina richiesta all'inizio non sarà contenuta in memoria, ma sarà contenuta su disco nello swap space di ogni processo (page fult da cold-start). Anche successivamente la pagina potrebbe non essere presente in memoria principale.

La posizione in MM e su disco può essere data dalla stessa tabella delle pagine.

# Gestione di un page fault - II

Se la MMU cercando nella tabella delle pagine identifica che la pagina cercata ha il bit di validità = 0 (pagina non ancora caricata), si genera un page fault.

Un page fault genera un'eccezione che deve essere gestita via software (dal SO). Come?

LRU approssimato. Use bit (Reference bit). Quando la MMU accede a quella pagina imposta lo use bit a 1. Periodicamente tutti gli use bit vengono azzerati.

In caso di page fault, la pagina virtuale viene trasferita in una pagina il cui Use bit  $\grave{e} = 0$ .

NB Lo use bit è differente dal bit di validità.

A. 2019-2020

24/5

# Dimensionamento di una tabella delle pagine

Indirizzi virtuali e fisici su 32 bit Dimensione della pagina di memoria di 32 Kbyte (2<sup>15</sup> Byte)

Numero di elementi della tabella delle pagine (numero di linee):

$2^{32} / 2^{15} = 2^{17}$  linee (ciascuna di 4 Byte  $\rightarrow$  indirizzi fisici su 4 Byte)

Tabella di ampiezza 4 Byte e altezza 128 K linee => 512 KByte

Abbiamo bisogno di 0.5 Mbyte per ogni processo attivo.

Cosa succede se abbiamo centinaia di processi?

Cosa succeede per indirizzi a 64 bit?

$2^{64} / 2^{15} = 2^{49}$  linee (ciascuna di 4 Byte) => 2 000 000 000 000 000 di Byte!

A.A. 2019-2020 25/53 http:\\borghese.di.unimi.it\

# Limitazione della tabella delle pagine

- Limitazione monodirezionale dell'altezza. Tabella virtuale di altezza limitata (numero max di linee cioe' di pagine virtuali). Possibilità di espandere in senso crescente.

- Limitazione bidirezionale dell'altezza. Memoria dati suddivisa in stack e heap. Crescono in

direzioni opposte => 2 tabelle delle pagine, una che ha indirizzi che crescono verso il basso e

una che ha indirizzi che crescono verso l'alto. Entrambe con nuero di linee limitato

(segmenti).

- Accesso indiretto. Altezza pari all'altezza della memoria fisica. Funzione di hashing per mappare l'indirizzo virtuale in indirizzo fisico. L'indirizzo virtuale non è più un indice ma diventa una chiave di accesso alla tabella.

- Tabella delle pagine gerarchica.

- Primo livello. Indicizza segmenti costituiti da un certo numero di pagine virtuali contigue (segment table).

- A) Il segmento contiene almeno una pagina caricata in MM.

- B) Il segmento non contiene pagine caricate in MM

- Nel caso A) la linea della segment table punta alla tabella delle pagine per quel segmento.

- Virtualizzazione della tabella delle pagine che viene inserita in memoria virtuale.

.A. 2019-2020 26/53 http:\\borghese.di.unimi.it\

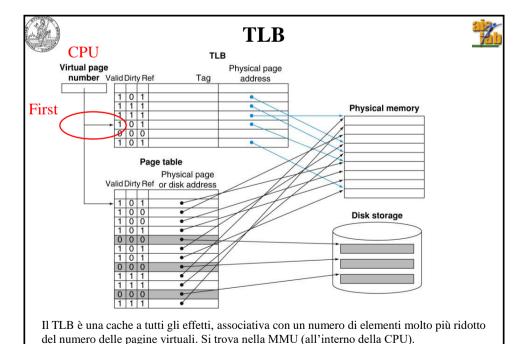

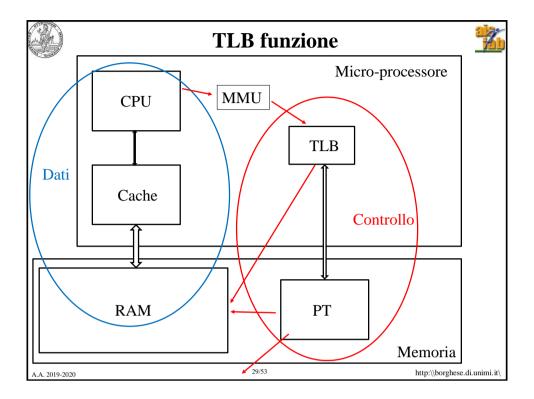

### IL TLB - Translation Lookaside buffer

http:\\borghese.di.unimi.it\

Con le PT (Tabelle delle pagine) ogni accesso alla memoria principale richiede in realtà **2** accessi (1 accesso alla PT + 1 accesso alla pagina).

Si sfrutta il principio di località: quando si accede al dato di una certa pagina, facilmente si avrà bisogno di un altro dato della stessa pagina. Si può evitare di dovere ritradurre una seconda volta l'indirizzo virtuale. Come?

Si introduce un buffer HW: **Translation Lookaside buffer** che memorizza le traduzioni (cache delle traduzioni):

- Dimensioni: 16-512 elementi (linee)

- Dimensione della linea (1-2 pagine, 4-8 byte ciascuna)

- Tempo di hit: 0,5-1 ciclo di clock

- Penalità di miss: 10-100 cicli di clock (per caricare la traduzione)

- Frequenza di miss: 0,01%-1%

A. 2019-2020

E.g. Nella libreria è come mantenere su un fogliettino la corrispondenza tra il numero d'ordine dei libri appena consultati e la loro posizione sugli scaffali della libreria.

A.A. 2019-2020 27/53 http://borghese.di.unimi.it/

28/53

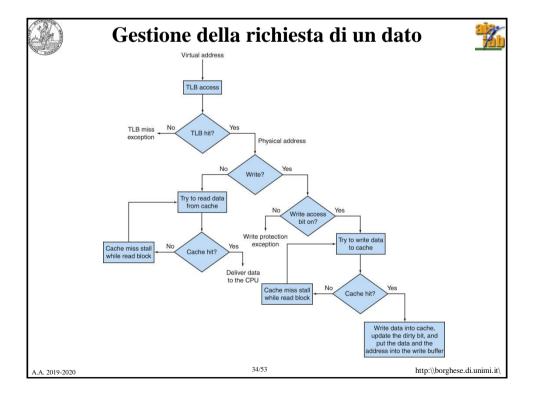

# Accesso alla memoria principale (hit in cache)

http:\\borghese.di.unimi.it\

1) Invio al TLB dell'indirizzo virtuale

Ho due situazioni:

- 1a) Indirizzo della pagina fisica è presente nel TLB (**hit del TLB** TAG = #pagina e valid = 1) Reference bit = 0/1

- Dirty bit = 1 (se accesso in scrittura).

- 1b) Miss -> Indirizzo della pagina fisica non è presente (miss del TLB).

Se ho una hit -> indirizzo fisico della memoria principale Lettura del micro-blocco e trasferimento in cache.

# Accesso alla memoria principale (miss in cache, ma hit in MM)

- 1) Invio al TLB dell'indirizzo virtuale

- 1b) Miss -> Indirizzo della pagina fisica non è presente (miss del TLB).

- Leggo la linea della tabella delle pagine usando come indice l'indirizzo virtuale e controllo il bit di validità.

- 2a) La traduzione è nella PT -> indirizzo fisico.

- 2b) La traduzione non è nella PT -> (page fault) -> indirizzo su disco.

- 2a) La traduzione è in MM

Carico nel TLB la traduzione dell'indirizzo virtuale se miss nel TLB

Trasferisco da MM a cache la linea richiesta.

A.A. 2019-2020 31/53 http:\\borghese.di.unimi.it\

# Accesso alla memoria principale (miss in cache e page fault)

- 1) Invio al TLB dell'indirizzo virtuale

- 1b) Miss -> Indirizzo della pagina fisica non è presente (miss del TLB).

- 2b) La traduzione non è nella PT -> (page fault).

### Nel caso di page fault:

- · Trasferisco da disco a MM la pagina richiesta

- Carico nella TB la traduzione dell'indirizzo della pagina virtuale.

Le miss del TLB sono più frequenti dei page fault.

### Gestione dei fallimenti

Miss nel TLB. Il TLB è una cache associativa. Sostituzione random. I bit di stato (valid, dirty, reference) vengono utilizzati per la politica di sostituzione delle pagine => quando scarico una linea del TLB nella PT devo aggiornare lo stato della pagina fisica. Se ho utilizzato di recente i dati di quella pagina quando erano in cache o li ho modificati deve risultare.

### Page fault.

Cercare la pagina virtuale nella tabella delle pagine e localizzare la pagina fisica corrispondente (su disco).

Scegliere una pagina fisica da sostituire; se la pagina fisica identificata ha il bit dirty = 1 (ci sono delle parole modificate), deve essere scritta su disco prima di caricare la nuova pagina nella memoria principale.

Iniziare il trasferimento della pagina da disco a memoria principale.

Aggiornare la traduzione della pagina virtuale nella pagina fisica all'interno dalla PT e reset del bit diry, set del bit di validità e di reference.

A.A. 2019-2020 33/53 http://borghese.di.unimi.it/

## Possibili situazioni in Cache, PT e TLB

| TLB  | Page<br>table | Cache | Possible? If so, under what circumstance?                                         |

|------|---------------|-------|-----------------------------------------------------------------------------------|

| Hit  | Hit           | Miss  | Possible, although the page table is never really checked if TLB hits.            |

| Miss | Hit           | Hit   | TLB misses, but entry found in page table; after retry, data is found in cache.   |

| Miss | Hit           | Miss  | TLB misses, but entry found in page table; after retry, data misses in cache.     |

| Miss | Miss          | Miss  | TLB misses and is followed by a page fault; after retry, data must miss in cache. |

| Hit  | Miss          | Miss  | Impossible: cannot have a translation in TLB if page is not present in memory.    |

| Hit  | Miss          | Hit   | Impossible: cannot have a translation in TLB if page is not present in memory.    |

| Miss | Miss          | Hit   | Impossible: data cannot be allowed in cache if the page is not in memory.         |

A.A. 2019-2020 35/53 http:\\borghese.di.unimi.it\

# Implementazione della protezione della MM<sup>a</sup>

Page Table page pointers are stored inside the OS space. They can be accessed only if OS is in Kernel mode.

We have to avoid that **a user process** (a virus) changes its own PT, **mapping one of its virtual pages into a physical page of a different process**. When accessing a physical page, a program should own that page.

This can be obtained by a personalized PT that can be addressed and modified by writing only by the OS. **Only reading the PT is granted to any user process**.

The write access bit can be used to protect the page from writing.

A process cannot read a page of another process because the mapping is contained inside its PT that has been written and is modified by the OS.

If a process wants to share a page with another process, the two virtual pages should point to the same physical page.

All these mechanisms are mediated by the OS in kernel mode.

\(\Lambda\). A. 2019-2020 \(36/53\) http:\\borghese.di.unimi.it\)

# **Changing process**

SO changes running process from P1 to P2 (context switch)

- Save the state of the CPU (registers, PC)

- Change the address of the Page Table from that of P1 to that of P2 (kernel mode operation)

- Invalidate the TLB (that is HW, to avoid to work on the physical pages of P1).

Upon restart of P1, we will have a lot of cold-start misses in the TLB.

NB We have 1 TLB but many PTs.

Per evitare lo svuotamento del TLB inutilmente:

- **Process identified or task identified** (field on 8 bits Intrinsity FASTMath MMU) added to the TAG field).

- Check for a hit is carried out on both the TAG and the process identifier fields (both in caches and in TLB).

A.A. 2019-2020 37/53 http://borghese.di.unimi.it/

### Sommario

Le virtual machine

La memoria virtuale

La traduzione degli indirizzi

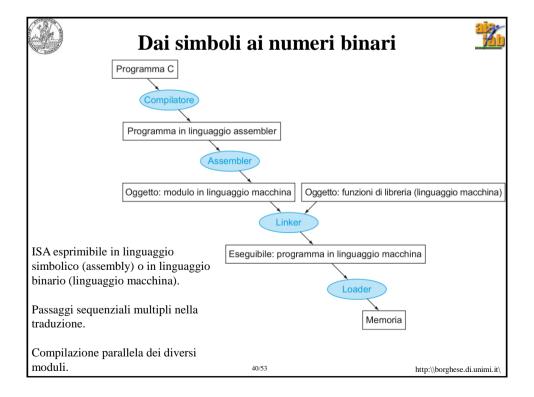

# Le istruzioni in linguaggio macchina

- Linguaggio di programmazione direttamente comprensibile dalla macchina

- Le parole di memoria sono interpretate come istruzioni

- Vocabolario è l'insieme delle istruzioni (instruction set)

Programma in linguaggio ad alto livello (C)

Programma in linguaggio macchina

A.A. 2019-2020 39/53 http:\\borghese.di.unimi.it\

# Dal codice sorgente al codice Assembler

http:\\borghese.di.unimi.it\

Compilatore: dal codice sorgente al codice Assembler.

Assemblatore: adatta il codice Assembler all'ISA (adattamento al «dialetto») dell'Architettura.

Assmblatore: codigica in linguaggio macchina (creazione del file oggetto), codifica binaria del codice.

Compilatore ed assemblatore possono essere uniti in un un'unica fase.

## L'assemblatore: i file oggetto

### L'assemblaggio produce:

- · L'insieme delle istruzioni in linguaggio macchina

- · I dati statici

- Le informazioni necessarie per inserire le istruzioni in memoria correttamente.

- Le informazioni necessarie per inserire I dati in memoria

#### Un file oggetto è così costituito:

- Header. Posizione e dimensione dei vari pezzi che costituiscono il file oggetto.

- Segmento testo. Contiene le istruzioni.

- Segmento dati statici. Contiene i dati relativi al file oggetto.

- Informazione di rilocazione. Identifica istruzioni, etichette e dati che dipendono dalla posizione del programma in memoria.

- La **tabella dei simboli.** Contiene le etichette che non sono definite (ad esempio riferimenti esterni, di altri moduli oggetto o librerie).

- Informazioni di debug. Consente di associare ai costrutti Assembler ai costrutti del linguaggio ad alto livello (la traduzione non è uno a uno).

A.A. 2019-2020 43/53 http:\\borghese.di.unimi.it

## Il linker (link editor)

Consente di fare ricompilare ed assemblare solo i moduli che vengono modificati (Rebuild).

### Il linker è costituito da 3 step:

- 1. Disporre in memoria i moduli di codice ed i dati (statici).

- 2. Identificare gli indirizzi dei dati e delle etichette delle istruzioni di salto.

- Risolvere le etichette interne ai moduli ed esterne (trovare la corrispondenza). Questo passo è equivalente a compilare una tabella di rilocazione.

Nei passi 2 e 3, il linker utilizza le informazioni di rilocazione degli oggetti e le tabelle dei simboli.

Quali sono i **simboli** da risolvere (da trasformare in indirizzi di memoria)?

- Etichette di salto (branch o jump)

- Indirizzo dei dati (e.g. A[0]).

Dopo avere risolto tutte le etichette (sostituito le corrispondenze), occorre trovare gli indirizzi assoluti associati alle etichette. Vengono cioè **rilocati** (riposizionati) gli oggetti al loro indirizzo finale.

Viene creato il file eseguibile. Ha lo stesso formato del file oggetto ma non ha riferimenti non risolti e gli indirizzi sono assoluti (virtuali -> rilocazione).

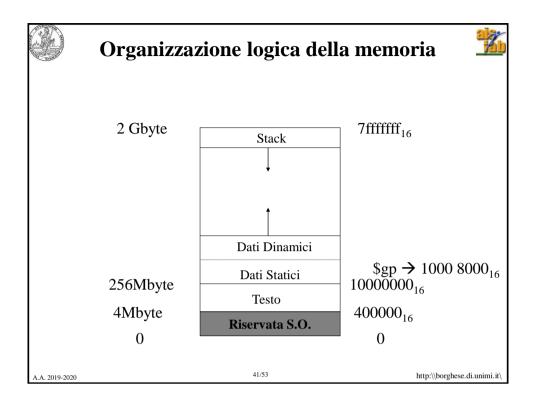

Dati Dinamici

Dati Statici

Testo

Riservata S.O.

A.A. 2019-2020 44/53 http://borghese.di.unimi.it/

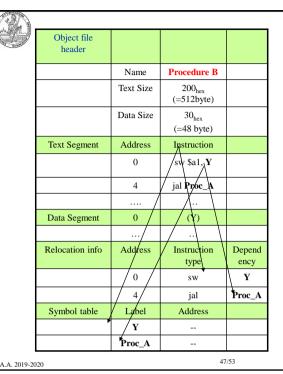

# Esempio

Analizziamo due procedure:

#### Procedure B Procedure A

0: Proc\_B: sw \$a1, 8000(\$gp) lw \$a0, **8000(\$gp)** 0: Proc\_A:

jal Proc\_B jal Proc\_A 4:

add \$t2, \$t1, \$t0

NB In questo caso \$gp punta a metà del primo segmento di 64Kbyte dell'area dati (256 Mbyte + 32Kbyte)

La tabella dei simboli contiene le etichette in grassetto.

### **Header Procedure A**

Text Size  $100_{\text{hex}}$  (=256byte)

**Header Procedure B** Text Size 200<sub>hex</sub> (=512byte)

Data Size  $20_{hex}$  (=32 byte) Data Size  $30_{hex}$  (=48byte)

45/53 http:\\borghese.di.unimi.it\ A.A. 2019-2020

46/53

| Object file<br>header |           |                               |                |

|-----------------------|-----------|-------------------------------|----------------|

|                       | Name      | Procedure A                   |                |

|                       | Text Size | 100 <sub>hex</sub> (=256byte) |                |

|                       | Data Size | 20 <sub>hex</sub> (=32 byte)  |                |

| Text Segment          | Address   | Instruction                   |                |

|                       | 0         | lw \$a0, <b>X</b> ∧           |                |

|                       | 4         | jal <b>Proc_B</b> $\lambda$   |                |

|                       |           | add \$t2, \$t1, \$t0          |                |

|                       |           | / / \                         |                |

| Data Segment          | 0         | / (x/)                        |                |

|                       |           | / / \                         |                |

| Relocation info       | Address   | Instruction type              | Depend<br>ency |

|                       | 0 /       | lw +                          | \ <b>x</b>     |

|                       | 4         | jal                           | Proc_B         |

| Symbol table          | Label /   | Address                       |                |

|                       | x * /     |                               |                |

|                       | Proc_B ▶  |                               |                |

.A. 2019-2020

# Oggetto proc A 🌋

http:\\borghese.di.unimi.it\

# Oggetto proc B 🐒

http:\\borghese.di.unimi.it\

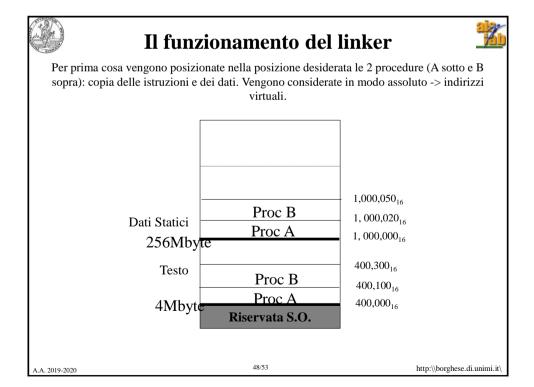

## Calcoli degli indirizzi testo

### Segmento testo:

Inizia dopo il segmento riservato al S.O., indirizzo  $0x400\ 000 = 0100\ 0000\ 0000\ 0000\ 0000\ 0000\ binario = 1x\ 2^{22} = 4$  Mbyte.

Procedura A. Inizia subito dopo. Indirizzo 0 della procedura è l'indirizzo 0x400 000.

Procedura B. Inizia dopo la procedura A. Indirizzo 0 della procedura B è:  $0x400\ 000 + 0x100$  (dimensione della procedura A) =  $0x400\ 100$ .

Queste osservazioni consentono di sostituire le etichette di salto a procedura (jal).

Analizziamo due procedure:

### Procedure A Procedure B

0: Proc\_A: lw \$a0, 8000(\$gp) 0: Proc\_B: sw \$a1, 8000(\$gp)

4: jal Proc\_B 4: jal Proc\_A

8: add \$t2, \$t1, \$t0 ...

A.A. 2019-2020 49/53 http://borghese.di.unimi.it/

### Risoluzione delle etichette sul codice

Text size =

$$100_{hex} + 200_{hex} = 300_{hex}$$

Data size =  $20_{hex} + 30_{hex} = 50_{hex}$

| Executable file header |           |                               |

|------------------------|-----------|-------------------------------|

|                        | Text Size | 300 <sub>hex</sub> (=768byte) |

|                        | Data Size | 50 <sub>hex</sub> (=82 byte)  |

| Text Segment           | Address   | Instruction                   |

| Proc A                 | 400,000   | lw \$a0, 8000(\$gp)           |

|                        | 400,004   | jal 400,100                   |

|                        | 400,008   | add \$t2, \$t1, \$t0          |

|                        |           |                               |

| Proc B                 | 400,100   | sw \$a1, 8000(\$gp)           |

|                        | 400,104   | jal 400,000                   |

|                        |           |                               |

| Proc B         |  |

|----------------|--|

| Proc A         |  |

|                |  |

| D D            |  |

| Proc B         |  |

| Proc A         |  |

| Riservata S.O. |  |

10, 000,020<sub>16</sub> 10, 000,000<sub>16</sub>

10,000,050<sub>16</sub>

400,300<sub>16</sub> 400,100<sub>16</sub> 400,000<sub>16</sub>

http:\\borghese.di.unimi.it\

A. 2019-2020 50/53

### Risoluzione delle etichette sui dati

| Executable file header |             |                               |

|------------------------|-------------|-------------------------------|

|                        | Text Size   | 300 <sub>hex</sub> (=768byte) |

|                        | Data Size   | 50 <sub>hex</sub> (=80 byte)  |

| Text Segment           | Address     | Instruction                   |

| Proc A                 | 400,000H    | lw \$a0, 8000( <b>\$gp</b> )  |

|                        | 400,004H    | jal 400,100                   |

|                        | 400,008H    | add \$t2, \$t1, \$t0          |

|                        |             |                               |

| Proc B                 | 400,100H    | sw \$a1, 8020( <b>\$gp</b> )  |

|                        | 400,104H    | jal 400,000                   |

|                        |             |                               |

| Data Segment           | Address     |                               |

|                        | 10,000,000H | (X)                           |

|                        | 10,000,020H | (Y)                           |

| Proc B Proc A                | 10,000,050 <sub>16</sub><br>10,000,020 <sub>16</sub><br>10,000,000 <sub>16</sub> |

|------------------------------|----------------------------------------------------------------------------------|

| Proc B Proc A Riservata S.O. | 400,300 <sub>16</sub><br>400,100 <sub>16</sub><br>400,000 <sub>16</sub>          |

A.A. 2019-2020

51/53

http:\\borghese.di.unimi.it\

A hash table

would help!

A. 2019-2020

# Dagli indirizzi virtuali agli indirizzi fisici

Dalla memoria su disco alla memoria principale (in quale pagina?)

Dipende da quali altri processi sono in esecuzione. Supponendo di:

Avere il segmento testo già preso fino all'indirizzo 100 Mbyte

- Avere il segmento dati preso fino ai 300 MByte.

- Avere pagine di 4 Kbyte

### Creazione dello spazio in memoria principale:

Posso allocare la prima pagina utile per il codice a 128 Mbyte (4K Byte > 768 Byte) Posso allocare la prima pagina utile per i dati a 512 Mbyte (4 Kbyte > 80 Byte)

- Allocazione della PT per il processo (4 MByte)

- Copia delle istruzioni e dei dati da disco alla memoria. In questa fase agli indirizzi virtuali dell'eseguibile vengono tradotti in indirizzi fisici, e la traduzione scritta nella tabella delle pagine.

La tabella delle pagine conterrà 2 elementi diversi da zero per questa procedura:

- 1) Linea 1,024 (4 Mbyte / 4 Kbyte) => 100 0000 0000 0000 0000 0000 0000 (128 MByte), indirizzo fisico della prima istruzione.

- 2) Linea 10 00 0000 0000 0000 (256 Mbyte / 4 Kbyte) =>

10 0000 0000 0000 0000 0000 00 00 0000 (512 MByte)

10 0000 0000 0000 (250 Mbyte / 4 Kbyte / ->

52/53 http:\\borghese.di.unimi.it\

# Sommario

Le virtual machine

La memoria virtuale

La traduzione degli indirizzi

A.A. 2019-2020 53/53 http:\\borghese.di.unimi.it\