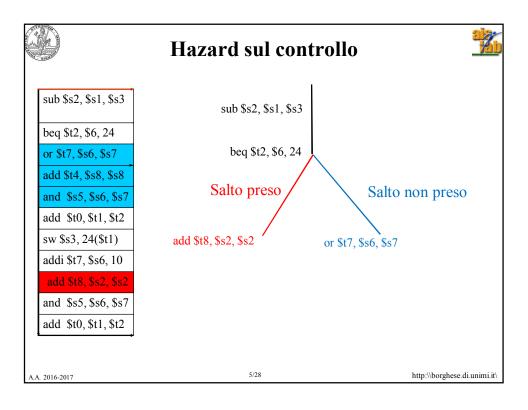

### Hazard sul controllo

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

alberto.borghese@unimi.it

Università degli Studi di Milano

Riferimento al Patterson: 4.7, 4.8

A.A. 2016-2017 1/28 http://borghese.di.unimi.it/

## Sommario

Riorganizzazione del codice (delay slot)

Esercizi

| Esempio di Hazard sul controllo |    |    |         |                |        |       |     |     |

|---------------------------------|----|----|---------|----------------|--------|-------|-----|-----|

| sub \$s2, \$s1, \$s3            | IF | ID | EX      | MEM            | WB     |       |     |     |

|                                 |    |    | \$1-\$3 |                | s->\$2 |       |     |     |

| beq \$t2, \$6, 24               |    | IF | ID      | EX             | MEM    | WB    |     |     |

|                                 |    |    |         | Zero if        | \      |       |     |     |

|                                 |    |    |         | (\$s2 == \$s5) | \      |       |     |     |

| or \$t7, \$s6, \$s7             |    |    | IF      | ID             | EX     | MEM   | WB  |     |

| add \$t4, \$s8, \$s8            |    |    |         | IF             | ID     | EX    | MEM | WB  |

| and \$s5, \$s6, \$s7            |    |    |         |                | IF     | ID ID | EX  | MEM |

| add \$t0, \$t1, \$t2            |    |    |         |                |        | IF    | ID  | EX  |

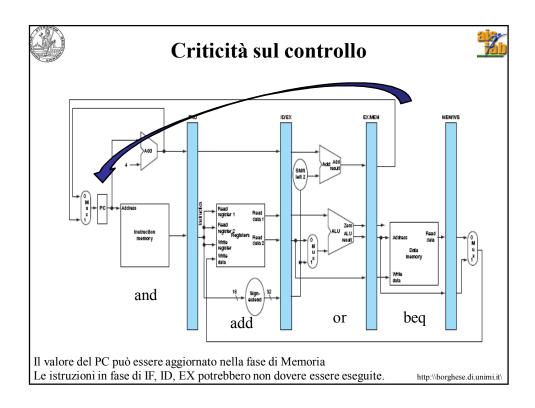

<u>In caso di salto:</u> dovrei avere disponibile all'istante in cui inizia l'esecuzione dell'istruzione or l'indirizzo dell'istruzione add e non eseguire la or, la add e la and.

NB L'indirizzo scritto nel PC corretto deve essere disponibile  $\underline{\text{prima}}$  dell'inizio della fase di fetch. Ho 3 istruzioni sbagliate in pipeline.

NB II PC è master/slave per cui occorre che l'indirizzo sia pronto prima dell'inizio della fase di fetch.

## Soluzioni alla criticità nel controllo

Modifiche strutturali per l'anticipazione dei salti. &

Riordinamento del codice (delayed branch).

A A 2012-2013 7/31 http://borghese.di.unimi.it

salta:

## Esempio di riorganizzazione del codice per le istruzioni di branch

```

if (a = b)

{ s2 = s0 + s1; } { s2 = s0 + s1; }

s3 = s4 + s5; } else

{ s3 = s4 + s5; }

s3 = s4 + s5; s6 = 2; s6 = 2;

```

A.A. 2012-2013 8/31 http://borghese.di.unimi.it

# Esempio di riorganizzazione del codice - II

```

if(a = = b)

if(a = = b)

s2 = s0 + s1;

s2 = s0 + s1;

s5 = s4 + s3;

}

else

else

t2 = t0 + t1;

t2 = t0 + t1;

s5 = s4 + s3;

s5 = s4 + s3;

t5 = 2;

t5 = 2;

```

http://borghese.di.unimi.it

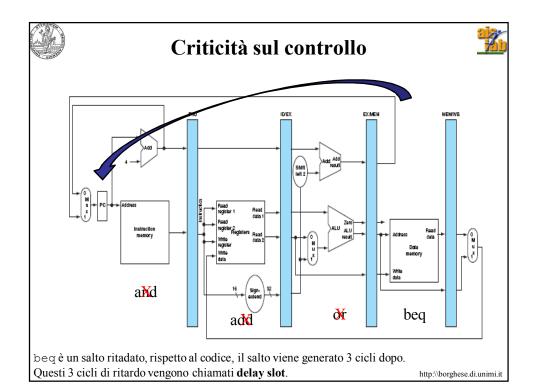

## Esempio di delayed branch (1 solo delay slot) 🌋

| Originale                                                                                                                                              | From targe                                                                               | et From before |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------|

| sub \$t5, \$t8, \$s8<br>add \$s4, \$t0, \$t1<br>beq \$s5, \$s6, salt<br>and \$s0, \$s0, \$s1<br>salto:<br>add \$t5, \$t4, \$t3<br>add \$t6, \$t7, \$t7 | sub \$t5, \$t8, \$add \$s4, \$t0, beq \$s5, \$s6, add \$t5, \$t4, and \$s0, \$s0, salto: | \$t1           |

L'istruzione add \$t5, \$t4, \$t3 o sub \$t5, \$t8, \$s8 viene comunque eseguita, il salto (se richiesto) avviene all'istante successivo.

Riempio quindi con queste istruzioni, istruzioni da eseguire comunque, lo slot dopo la banch, denominato branch delay slot.

Controllo di non inserire Hazard sui dati

http:\\borghese.di.unimi.it

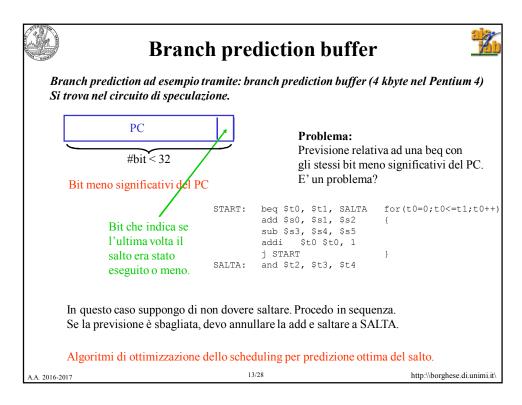

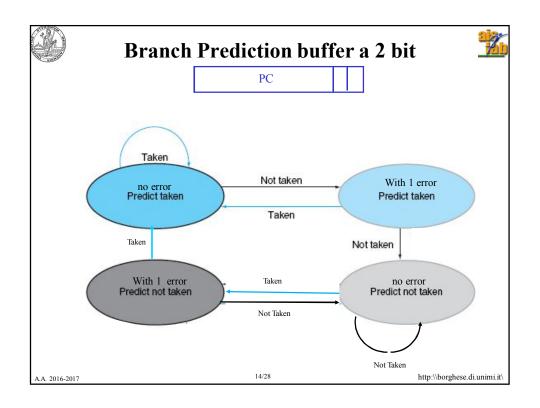

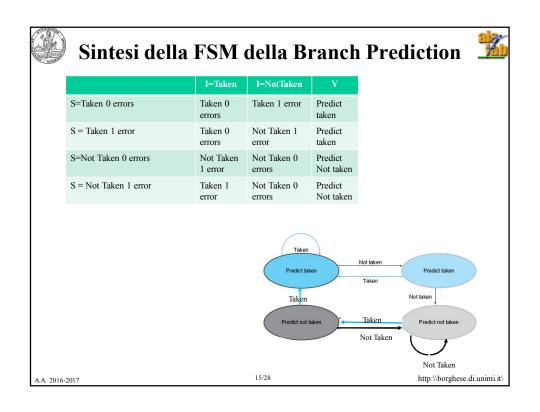

### Evoluzioni della branch prediction

- Correlating predictors. Comportamento locale e globale dei salti. Tipicamente 2 predittori a 2 bit. Viene scelto il predittore che correla meglio con la storia del salto.

- 2) Tournament predictors. Vengono utilizzati predittori multipli a 1 o 2 bit, e per ogni branch viene selezionato il predittore migliore. Il selettore selezione quale dei due bit di informazione utilizzare, in base alla loro accuratezza di predizione. Solitamente viene utilizzato un predittore che analizza informazioni locali (di contesto), un altro che analizza informazioni globali (di contesto). Informazioni di contesto possono ad esempio essere contenuto di registri.... Il codice di selezione per il selettore viene memorizzato del branch prediction buffer.

A.A. 2016-2017 17/28 http://borghese.di.unimi.it/

#### Salto incondizionato

Utilizzato all'interno dei cicli for / while. Non pone problemi. Si risolve con la riorganizzazione del codice

400: add \$s0, \$s1, \$s2 400: j 80004

404: j 80000 404: add \$s0, \$s1, \$s2 Label 408: and \$s1, \$s2, \$s3 408: and \$s2, \$s2, \$s3

> 80000: or \$t0, \$t1, \$t2 80000: or \$t0, \$t1, \$t2 80004: sub \$t3, \$t4, \$t5 80004: sub \$t3, \$t4, \$t5

j "lavora" nella fase di decodifica. Viene eseguita un'istruzione prima del salto: delayed jump. Riempio tutti gli slot di esecuzione.

L'esecuzione avviene fuori ordine, ma l'utente non vede differenze.

Come viene modificata la CPU (parte di datapath e parte di controllo)?

A.A. 2016-2017 18/28 http://borghese.di.unimi.it/

## Salto incondizionato – soluzione II

Prendo l'istruzione dalla destinazione del salto.

400: add \$s0, \$s1, \$s2 400: add \$s0, \$s1, \$s2

404: j 80000 404: j 80004

Label 408: and \$s1, \$s2, \$s3 408: or \$t0, \$t1, \$t2

> and \$s2, \$s2, \$s3 412:

80000: or \$t0, \$t1, \$t2 80004: sub \$t3, \$t4,\$t5

80004: sub \$t3, \$t4, \$t5

Riempio tutti gli slot di esecuzione.

L'assemblatere (ri)ordina il codice.

http:\\borghese.di.unimi.it\

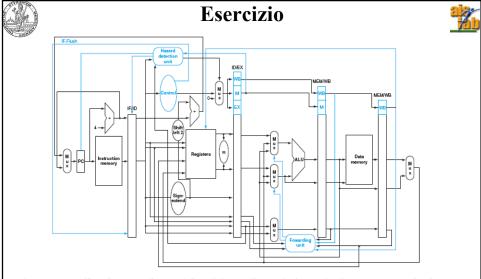

Data la CPU sopra, specificare il contenuto di TUTTE le linee (dati e controllo) quando è in esecuzione il seguente segmento di codice: 0x400 addi \$t3, \$t1, 32

0x400 add \$15, \$11, \$2 0x404 sub \$14, \$11, \$11 0x408 add \$11, \$12, \$13 0x 40C beq \$11, \$50, 40 0x410 sw \$\$2, 64(\$\$0)

quando l'istruzione di addi si trova in fase di WB. Specificare sullo schema (con colore o con tratto grosso) quali linee, all'interno dei diversi stadi, trasportino dati e segnali di controllo utili all'esecuzione dell'istruzione, riferendosi alla situazione in cui l'istruzione di addi è in fase di

## Sommario

$http: \! \backslash borghese.di.unimi.it \! \backslash$

Riorganizzazione del codice (delay slot)

Esercizi