## Unità di controllo della pipeline

Prof. Alberto Borghese Dipartimento di Informatica

<u>borghese@di.unimi.it</u>

Università degli Studi di Milano

Riferimento al Patterson: 4.5, 4.6

A.A. 2012-2013 1/15 http://borghese.di.unimi.it/

#### Sommario

La CPU con pipeline

L'Unità di Controllo della pipeline

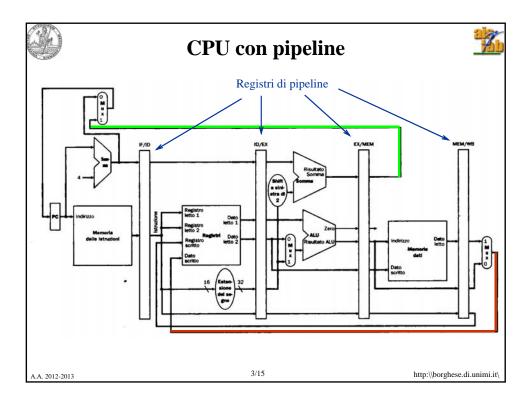

#### Gli stadi di esecuzione

EX/MEM

MEM/WB

- $IF-Instruction\ Fetch$

- ID Instruction Decode (e lettura register file)

- EX Esecuzione o calcolo dell'indirizzo di memoria.

- MEM Accesso alla memoria dati.

- WB Write Back (scrittura del risultato nel register file).

NB: I registri al termine di ogni fase prendono il nome dalle 2 fasi:

IF/ID ID/EX

Perchè non c'è un registro WB/IF?

Il data-path procede da sx a dx.

## Il ruolo dei registri

Ciascuno stadio produce un risultato. La parte di risultato che serve agli stadi successivi deve essere memorizzata in un registro.

Il registro mantiene l'informazione anche se lo stadio in questione riutilizza l'unità funzionale.

Esempio: l'istruzione letta viene salvata nel registro IF/ID (cf. Instruction Register).

A.A. 2012-2013 5/15

## Esempio di esecuzione

http:\\borghese.di.unimi.it\

Cosa si trova nella pipeline durante l'esecuzione di questo segmento di codice (dati + controllo)?

| 0x4000 | lw \$t1, 24(\$t2)    | WB  |

|--------|----------------------|-----|

| 0x4004 | sw \$t2, 36(\$t1)    | M   |

| 0x4008 | beq \$t1, \$s2, 20   | EX  |

| 0x400C | add \$s0, \$t1, \$s2 | DEC |

| 0x4010 | sub \$t0, \$t1, \$t2 | FF  |

| 0x4014 | or \$s3, \$t4, \$t5  |     |

NB Occorre specificare il contenuto della parte master e slave dei registri di pipeline.

Data path che fluisce da sinistra a destra.

I registri letti dal register file sono specificati nella fase di ID, quello scritto nella fase di WB.

A.A. 2012-2013 6/15 http://borghese.di.unimi.it/

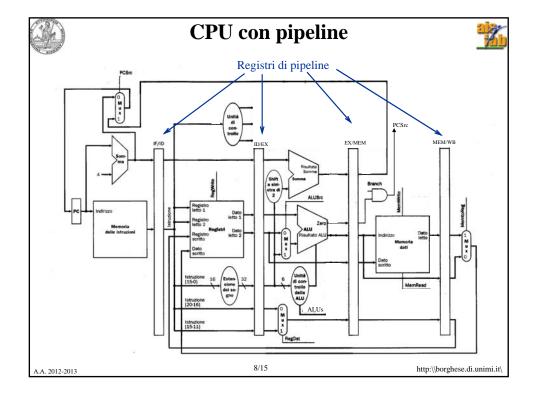

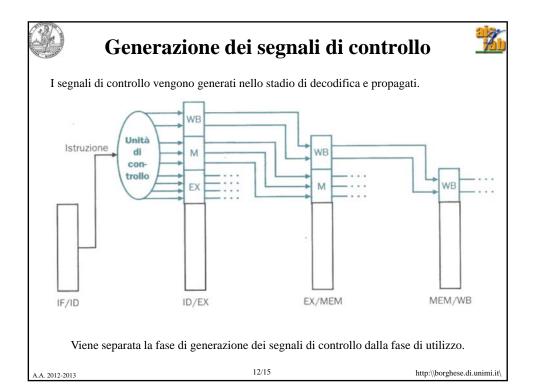

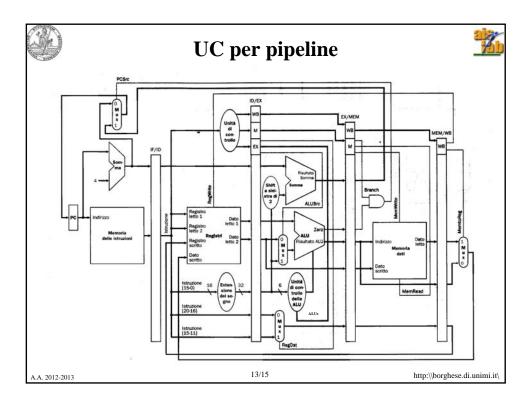

# La UC della CPU con pipeline

Definizione dei segnali di controllo per ogni stadio, per ogni istruzione.

Definizione dell'UC in grado di generare correttamente questi segnali.

A.A. 2012-2013 9/15 http://borghese.di.unimi.it/

| Segnali di controllo su 1 bit |                                                                                                                     |                                                                                                                                            |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Nome segnale                  | Effetto quando è negato                                                                                             | Effetto quando è affermato                                                                                                                 |  |  |  |  |

| RegDst                        | Il numero del registro destinazione proviene dal campo rt (R2, bit 20-16)                                           | Il numero del registro destinazione proviene<br>dal campo rd (bit 15-11)                                                                   |  |  |  |  |

| RegWrite                      | Nessuno                                                                                                             | Nel registro specificato all'ingresso registro<br>scritto del Register File, viene scritto il<br>valore presente all'ingresso Dato Scritto |  |  |  |  |

| ALUSrc                        | Il secondo operando della ALU<br>proviene dalla seconda uscita in lettura<br>del Register File                      | Il secondo operando della ALU è la versione estesa (con segno) del campo offset                                                            |  |  |  |  |

| Branch                        | Il valore del PC viene sostituito<br>dall'uscita del sommatore che calcola<br>PC+4 (condizionato all'uscita di ALU) | Il valore del PC viene sostituito dall'uscita<br>del sommatore che calcola la destinazione<br>del salto (condizionato all'uscita di ALU)   |  |  |  |  |

| MemRead                       | Nessuno                                                                                                             | Il contenuto della cella di memoria dati<br>indirizzata dal MAR è posto nel MDR                                                            |  |  |  |  |

| MemWrite                      | Nessuno                                                                                                             | Il contenuto in ingresso al MDR, viene<br>memorizzato nella cella il cui indirizzo è<br>caricato nel MAR                                   |  |  |  |  |

| MemtoReg                      | Il valore inviato all'ingresso Dato al<br>Register File proviene dalla ALU                                          | Il valore inviato all'ingresso Dato al Register<br>File proviene dalla memoria                                                             |  |  |  |  |

Scrittura PC e scrittura dei registri di pipeline ad ogni fronte di clock (ad ogni stadio).

A.A. 2012-2013 10/15 http:\\borghese.di.unimi.it\

#### Osservazioni

Il contenuto di *rt* ed il numero di scrittura nel Register File (*rd*) vengono portati attraverso i vari stadi.

Nella fese di fetch e di decodifica non esistono segnali di controllo particolari.

I segnali di controllo particolari (legati alle diverse istruzioni) si possono così raggruppare:

|            | Exec       |       |       | Memory     |        | WB          |              |              |             |

|------------|------------|-------|-------|------------|--------|-------------|--------------|--------------|-------------|

| Istruzione | Reg<br>Dst | ALUs1 | ALUs0 | ALU<br>Src | Branch | Mem<br>Read | Mem<br>Write | Reg<br>Write | Mem2<br>Reg |

| Format-R   | 1          | 1     | 0     | 0          | 0      | 0           | 0            | 1            | 0           |

| lw         | 0          | 0     | 0     | 1          | 0      | 1           | 0            | 1            | 1           |

| sw         | X          | 0     | 0     | 1          | 0      | 0           | 1            | 0            | X           |

| beq        | X          | 0     | 1     | 0          | 1      | 0           | 0            | 0            | X           |

## Esempio di esecuzione

Cosa si trova nella pipeline durante l'esecuzione di questo segmento di codice (dati + controllo)?

lw \$t1, 24(\$t2) add \$s0, \$t1, \$s2 beq \$t1, \$s2, 20 sw \$t2, 36(\$t1) sub \$t0, \$t1, \$t2 or \$s3, \$t4, \$t5

NB Occorre specificare il contenuto della parte master e slave dei registri di pipeline.

I segnali di controllo fluiscono anch'essi da sinistra verso destra.

Il segnale di scrittura nel register file viene generato nella fase ID ma viene consumato nella fase WB.

Il segnale di scrittura nel register file proviene dalla fase di WB.

.A. 2012-2013 14/15 http://borghese.di.unimi.it/

# Sommario

$http: \hspace{-0.05cm} \ \ | borghese.di.unimi.it \rangle$

La CPU con pipeline

L'Unità di Controllo della pipeline

A 2012-2013 15/15