# Architettura degli elaboratori - II CPU a ciclo singolo

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

borghese@dsi.unimi.it

Università degli Studi di Milano

Riferimento sul Patterson: capitolo 4.2, 4.4, D1, D2.

A.A. 2011-2012

1/35

$http: \\ \ \ homes.dsi.unimi.it \\ \ \ \ \ \ borghese$

## **Sommario**

### La CPU

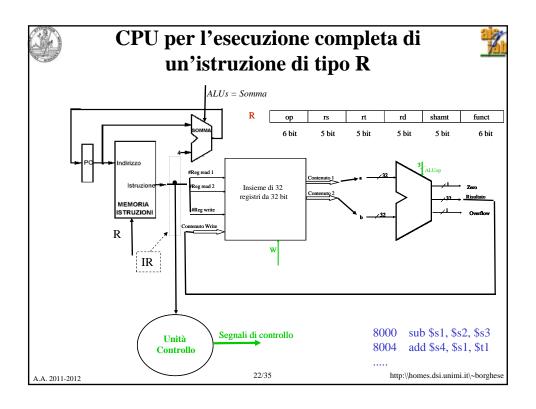

Costruzione di una CPU per le istruzioni di tipo R

Costruzione di una CPU per le istruzioni di tipo I (memoria).

A.A. 2011-2012

2/35

$http: \\ \ homes.dsi.unimi.it \\ \ \ \ \ borghese$

## I componenti di un'architettura

#### **CPU**

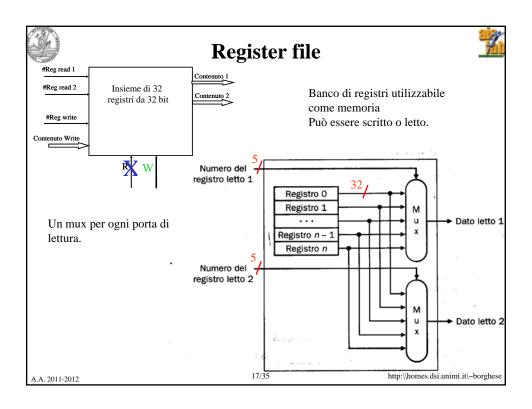

- Banco di registri (Register File) ad accesso rapido, in cui memorizzare i dati di utilizzo più frequente. Il tempo di accesso ai registri è circa 10 volte più veloce del tempo di accesso alla memoria principale.

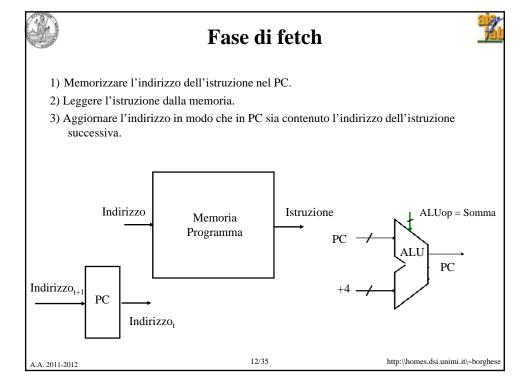

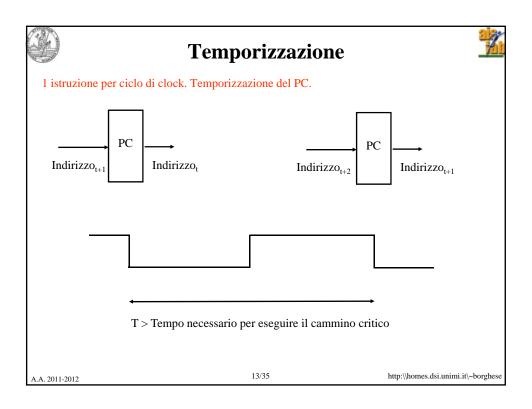

- Registro *Program counter (PC)*. Contiene l'indirizzo dell'istruzione corrente da aggiornare durante l'evoluzione del programma, in modo da prelevare dalla memoria la corretta sequenza di istruzione;

- Registro *Instruction Register (IR)*. Contiene l'istruzione in corso di esecuzione. Questo registro verrà utilizzato più avanti nelle architetture multi-ciclo.

- Unità per l'esecuzione delle operazioni aritmetico-logiche (Arithmetic Logic Unit ALU). I

dati forniti all'ALU possono provenire da registri oppure direttamente dalla memoria, a

seconda delle modalità di indirizzamento previste;

- Unità aggiuntive per elaborazioni particolari come unità aritmetiche per dati in virgola mobile (Floating Point Unit – FPU), sommatori ausiliari, ecc.;

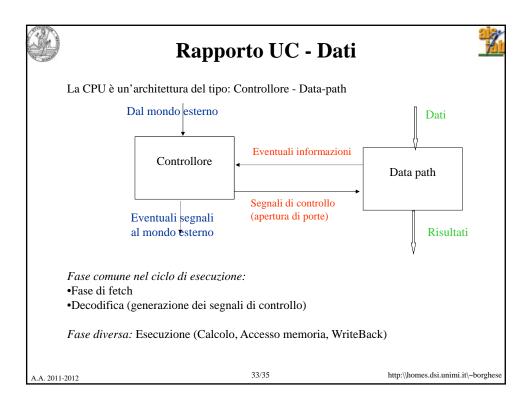

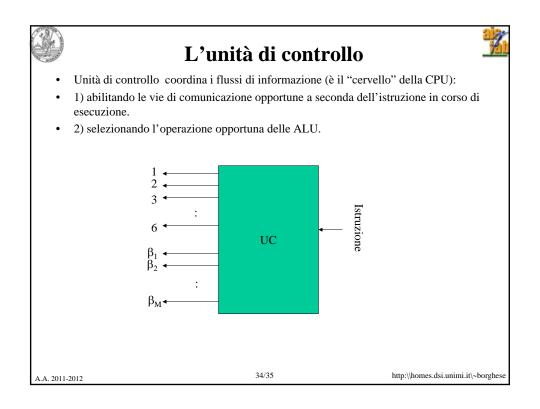

- Unità di controllo. Controlla il flusso e determina le operazioni di ciascun blocco.

#### MEMORIA PRINCIPALE

A.A. 2011-2012 4/35 http:\\homes.dsi.unimi.it\~borghes

- Tutte le istruzioni MIPS hanno la stessa dimensione (32 bit) Architettura RISC.

- I 32 bit hanno un significato diverso a seconda del formato (o tipo) di istruzione

- il tipo di istruzione è riconosciuto in base al valore di alcuni bit (6 bit) più significativi (codice operativo - OPCODE)

- Le istruzioni MIPS sono di 3 tipi (formati):

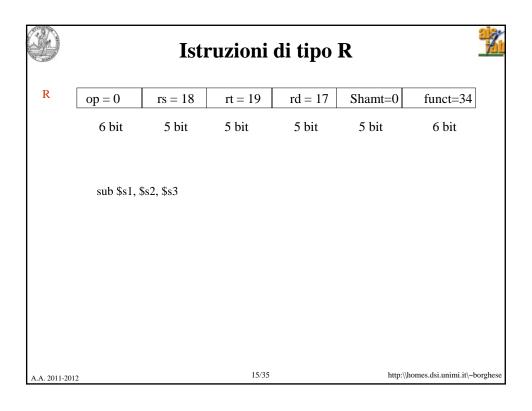

- Tipo R (register) Lavorano su 3 registri.

- Istruzioni aritmetico-logiche.

- Tipo I (immediate) Lavorano su 2 registri. L'istruzione è suddivisa in un gruppo di 16 bit contenenti informazioni + 16 bit riservati ad una costante.

- · Istruzioni di accesso alla memoria o operazioni contenenti delle costanti.

- Tipo J (jump) Lavora senza registri: codice operativo + indirizzo di salto.

- Istruzioni di salto incondizionato.

|   | 6-bit | 5-bit     | 5-bit | 5-bit     | 5-bit | 6-bit |  |  |  |

|---|-------|-----------|-------|-----------|-------|-------|--|--|--|

| R | ор    | rs        | rt    | rd        | shamt | funct |  |  |  |

| I | ор    | rs        | rt    | indirizzo |       |       |  |  |  |

| J | ор    | indirizzo |       |           |       |       |  |  |  |

A.A. 2011-2012 5/35 http:\\homes.dsi.unimi.it\~borghese

## Istruzioni

| add \$s1, \$s2, \$s3                      | 000000 | 10010 | 10011 | 1000 | 1 00 | 0000 | 100000 |  |

|-------------------------------------------|--------|-------|-------|------|------|------|--------|--|

| beg \$s1, \$s2, -100                      | 000100 | 10001 | 10010 | 1111 | 1111 | 1110 | 0111   |  |

| 204 422, 422, 200                         | 000100 | 10001 | 10010 |      |      | 1110 | 0111   |  |

| lw \$t0, 32 (\$s3)                        | 100011 | 10011 | 01000 | 0000 | 0000 | 0010 | 0000   |  |

| sw \$t0, 32 (\$s3)                        | 101011 | 10011 | 01000 | 0000 | 0000 | 0010 | 0000   |  |

| addi \$t0, \$s3, 64                       | 001000 | 10011 | 01000 | 0000 | 0000 | 0100 | 0000   |  |

| j 0x80000 000010 00 0000 0100 0000 0000 0 |        |       |       |      |      |      |        |  |

A.A. 2011-2012 6/35 http://homes.dsi.unimi.it/~borghese

## **Sommario**

La CPU

Costruzione di una CPU per le istruzioni di tipo R

Costruzione di una CPU per le istruzioni di tipo I (memoria).

A.A. 2011-2012

7/35

http:\\homes.dsi.unimi.it\~borghes

## **Obbiettivo**

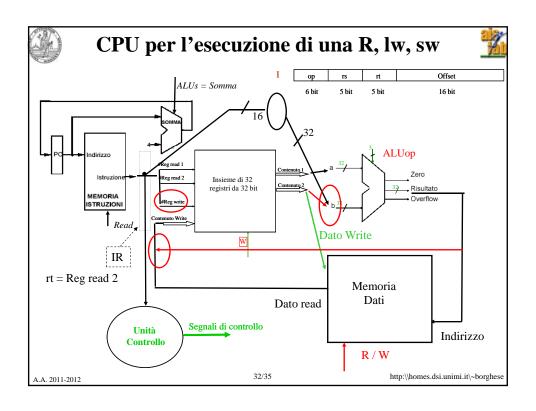

Costruzione di una CPU completa che sia in grado di eseguire:

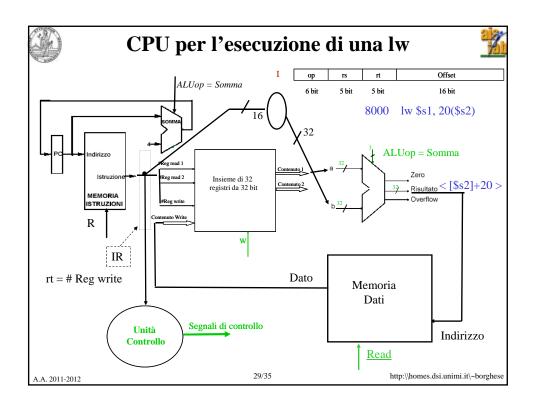

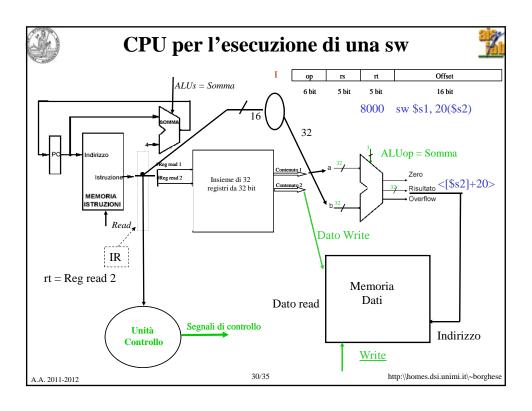

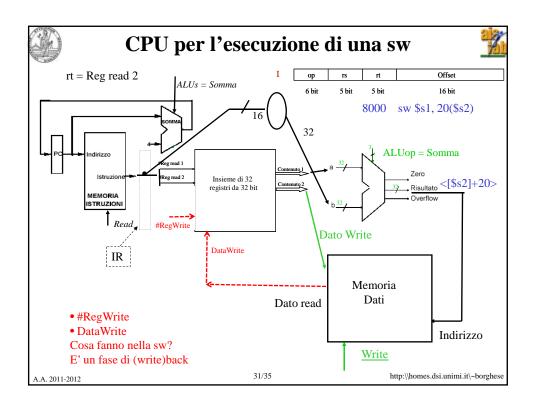

- Accesso alla memoria in lettura (lw) o scrittura (sw).

- Istruzioni logico-matematiche (e.g. add, sub, and....).

- Istruzioni di salto condizionato (branch) o incondizionato (jump).

A.A. 2011-2012

8/35

$http: \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} http: \hspace{-0.05cm} \hspace{-0.05c$

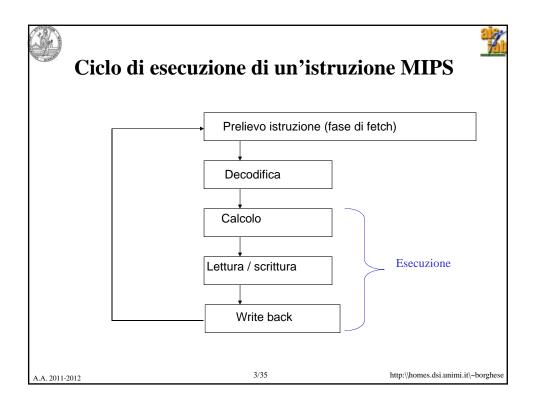

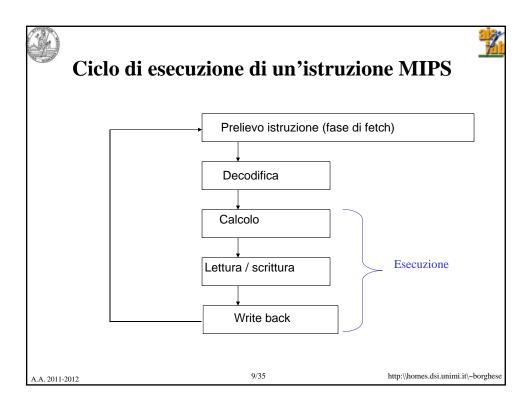

## Come funziona una CPU?

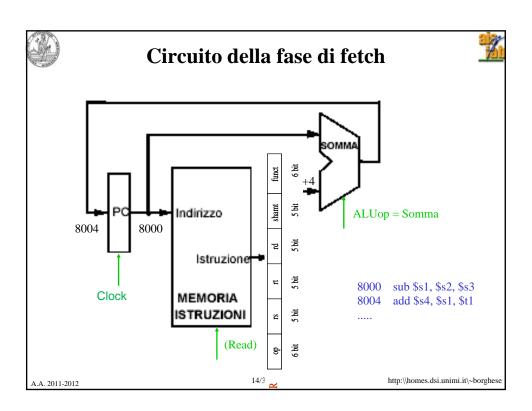

- Usa un registro, il Program Counter (PC) per ottenere l'indirizzo dell'istruzione.

- Preleva l'istruzione dalla memoria e la inserisce nell'IR.

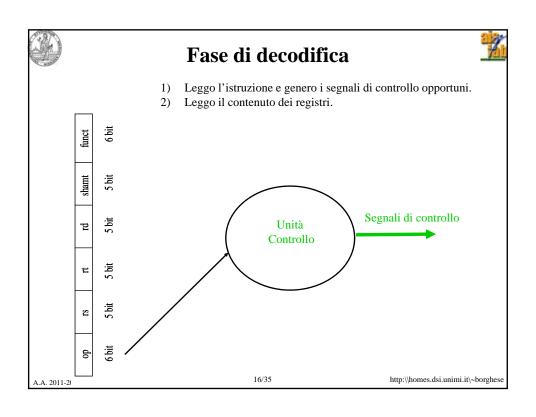

- Capisce di che tipo di istruzione si tratta (decodifica).

- usa l'istruzione stessa per decidere cosa fare esattamente.

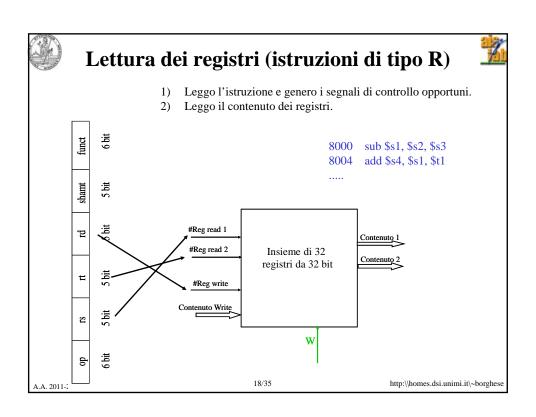

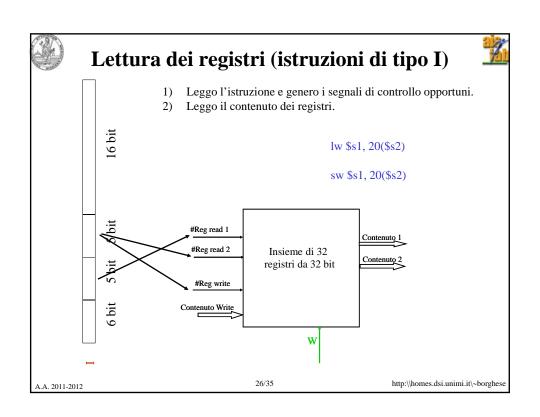

- Legge il contenuto dei registri.

#### Da qui le istruzioni si differenziano.

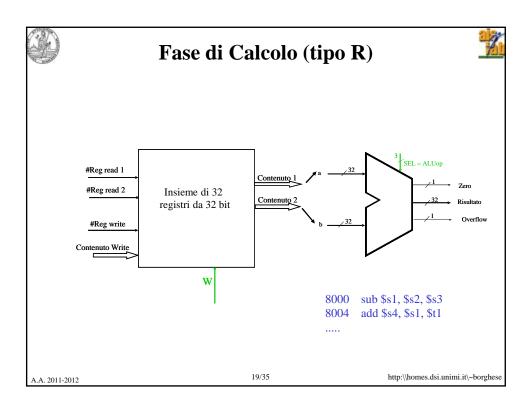

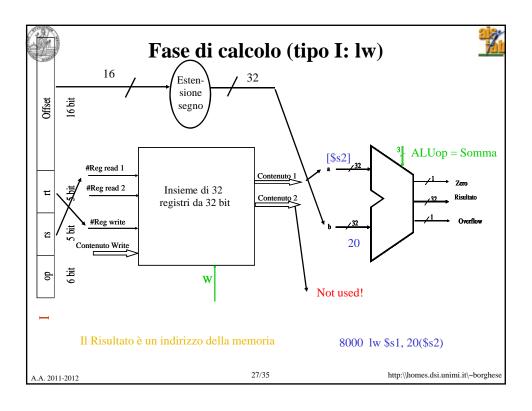

- Calcolo: utilizzo dell'ALU dopo aver letto i registri:

- per calcolare l'indirizzo in memoria.

- per eseguire un'operazione logico-aritmetica.

- per effettuare test (uguaglianza, disuguaglianza, <...).

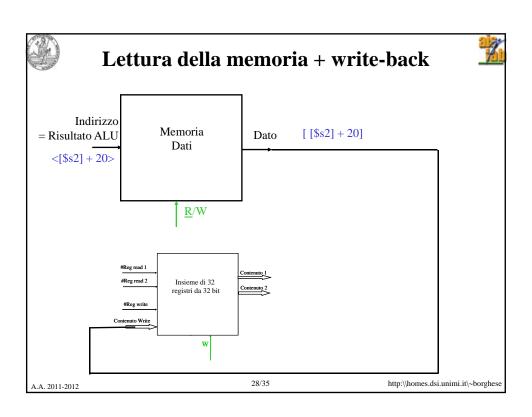

- Accesso alla memoria.

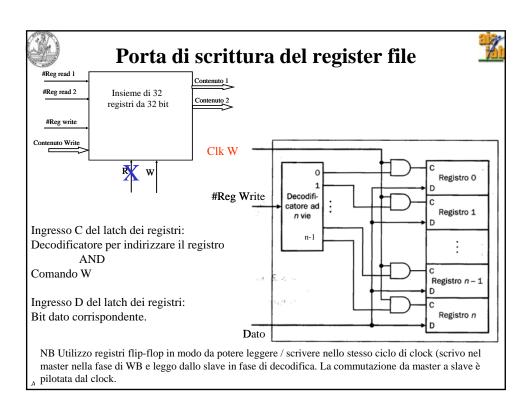

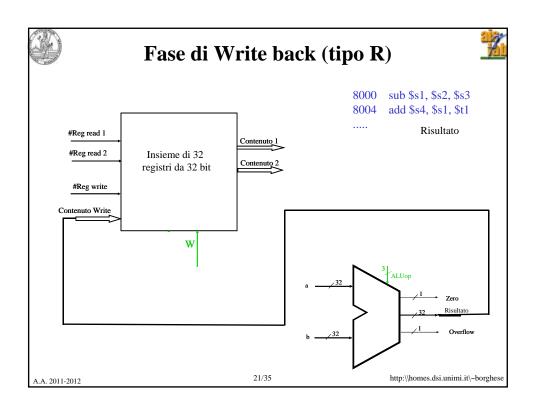

- Scrittura del risultato nel register file.

A.A. 2011-2012 10/35 http:\\homes.dsi.unimi.it\~borghese

### Come funziona una CPU?

- Usa un registro, il Program Counter (PC) per ottenere l'indirizzo dell'istruzione.

- Preleva l'istruzione dalla memoria e la inserisce nell'IR.

- Capisce di che tipo di istruzione si tratta (decodifica).

- usa l'istruzione stessa per decidere cosa fare esattamente.

- Legge il contenuto dei registri.

#### Da qui le istruzioni si differenziano.

- Calcolo: utilizzo dell'ALU dopo aver letto i registri:

- per calcolare l'indirizzo in memoria.

- per eseguire un'operazione logico-aritmetica.

- per effettuare test (uguaglianza, disuguaglianza, <...).

- Accesso alla memoria.

- <sup>n</sup> Scrittura del risultato nel register file.

A.A. 2011-2012

11/35

http:\\homes.dsi.unimi.it\~borghese

## **Sommario**

La CPU

Costruzione di una CPU per le istruzioni di tipo R

Costruzione di una CPU per le istruzioni di tipo I (memoria).

A.A. 2011-2012

23/35

http:\\homes.dsi.unimi.it\~borghese

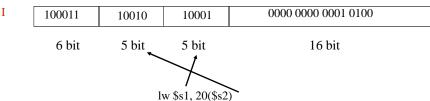

# Istruzioni di tipo I: lw/sw

L'indirizzo di memoria sarà:

Indirizzo dato 0100 1000 0011 0001 1011 1011 1100 1111

A.A. 2011-2012

24/35

$http: \\ \ homes.dsi.unimi.it \\ \ \sim borghese$

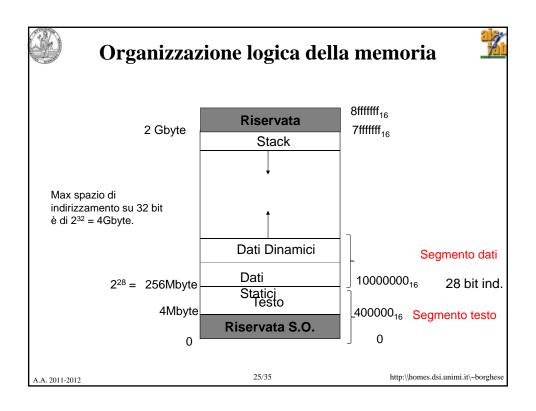

## Sommario

Costruzione di una CPU per le istruzioni di tipo R

Costruzione di una CPU per le istruzioni di tipo I (memoria).

Costruzione di una CPU per le istruzioni di tipo I (salti).

A.A. 2011-2012 35/35 http:\\homes.dsi.unimi.it\~borghes