Cognome e nome dello studente:

Matricola:

Versione B

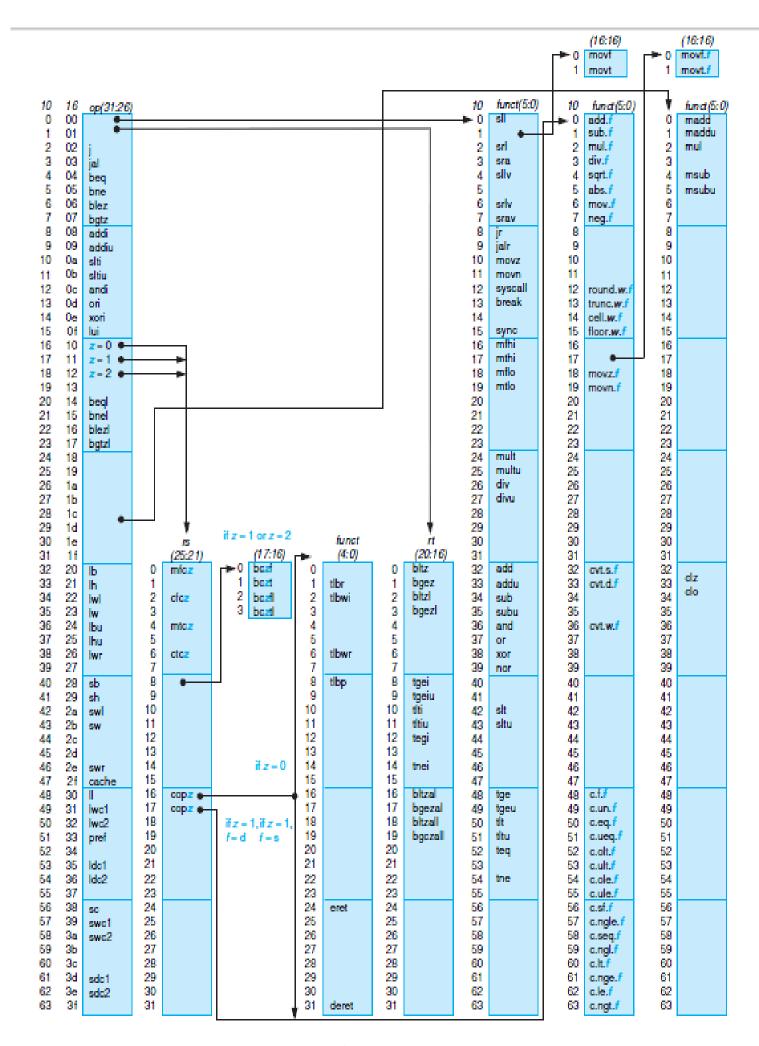

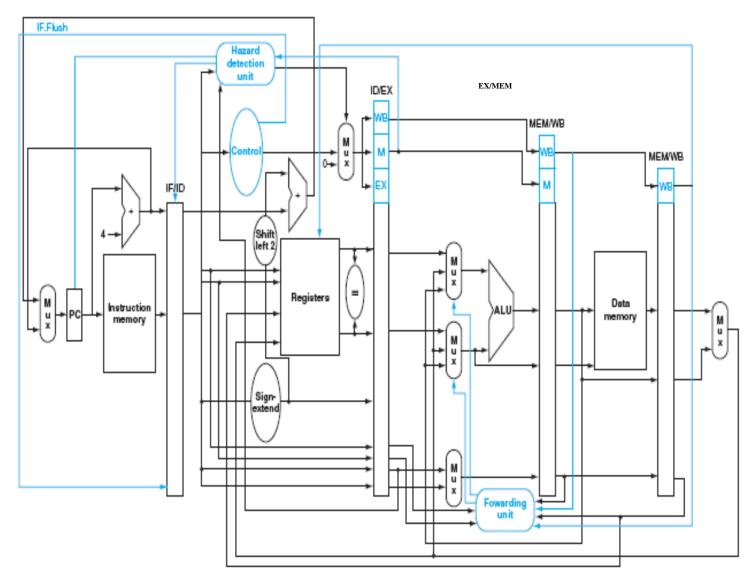

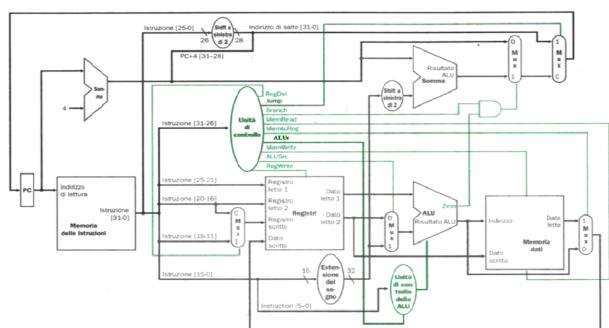

1. [8] Data la CPU sopra, specificare il contenuto di TUTTE le linee (dati e controllo) quando è in esecuzione il seguente segmento di codice [5]:

slti \$t4, \$t1, 24

and \$t3, \$t2, \$t4

addi \$t1, \$t4, 64

addi \$t1, \$t3, 10

sw \$s2, 32(\$s0)

quando l'istruzione di slti (set on less than immediate) si trova in fase di WB. Specificare sullo schema (con colore o con tratto grosso) quali linee, all'interno dei diversi stadi, trasportino dati utili all'esecuzione dell'istruzione nello stadio corrente, riferendosi alla situazione in cui l'istruzione di slti è in fase di WB. Sia in questo esercizio che negli esercizi successivi potete modificare / aggiungere componenti allo schema [3].

2. [5] Quando si verificano degli hazard sul controllo? Fare un esempio di codice con hazard sul controllo e spiegare come possono essere gestiti da una CPU. Identificare l'hazard sul controllo nel codice riportato sotto, modifica del codice riprotato per l'esercizio 1, ed eventualmente modificare la CPU per gestirlo correttamente.

slti \$t4, \$t1, 24

and \$t3, \$t2, \$t4

addi \$t1, \$t4, 64

beq \$t1, \$t3, 20

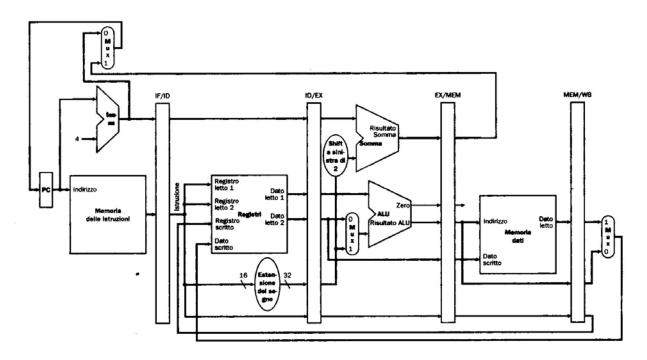

3. [4] Modificare la CPU con pipeline di base riportata sotto, in modo che esegua correttamente le istruzioni di ori, tralasciando gli hazard sui dati. Inserire eventuali modifiche ed i segnali di controllo.

- 4. [6] Cos'è un hazard? Cos'è uno stallo? Stallo e bolla sono la stessa cosa? Si verificano hazard nell'esecuzione del codice precedentedell'esercizio 1? Motivare la risposta. Disegnare il circuito della Hazard Detection Unit utilizzando le porte logiche.

- 5. [2] Come viene eseguita una istruzione di Jump in una pipeline?

- 6. [4] Come funziona un branch prediction buffer a 2 bit? Qual'è il suo ruolo? A cosa serve? Quali tecniche conoscete per limitare l'impatto di un Hazard sul controllo? Cos'è un flush della pipeline? Che differenza c'è tra inserire una bolla ed effettuare il flush di una pipeline?

- 7 [6] Identificare i cammini attivi quando viene eseguita un'istruzione di beq nella CPU a singolo ciclo riportata sotto. E' corretto definire un cammino critico per questa CPU? Quali istruzioni riguarderà e perchè? Come verrà eventualmente calcolato? Quali tipi di bistabili vengono utilizzati per i diversi componenti che hanno una memoria?

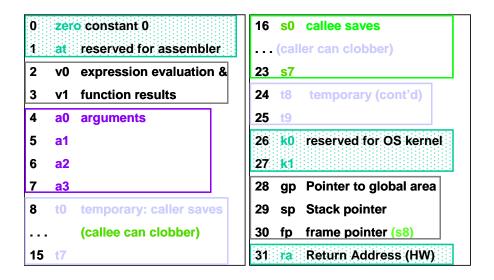

## Registri del register file