### Latch sincroni e flip-flop

Prof. Alberto Borghese Dipartimento Informatica

borghese@di.unimi.it

Università degli Studi di Milano

Riferimento Patterson: sezioni B.7 & B.8.

A.A. 2017-2018 1/33 http://borghese.di.unimi.it/

### **Sommario**

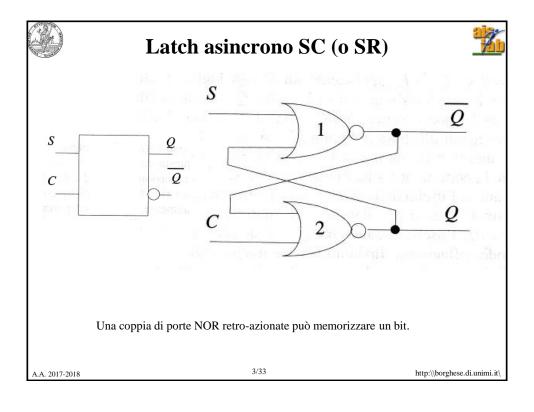

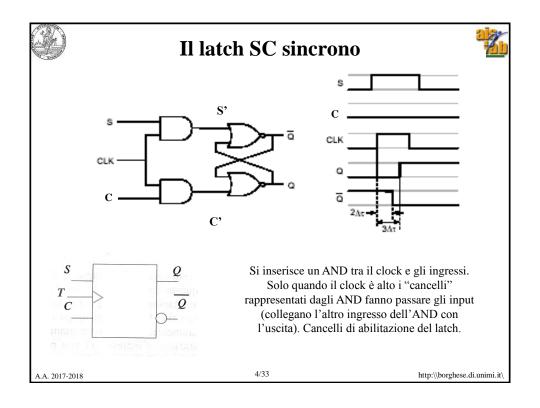

Latch sincroni SR

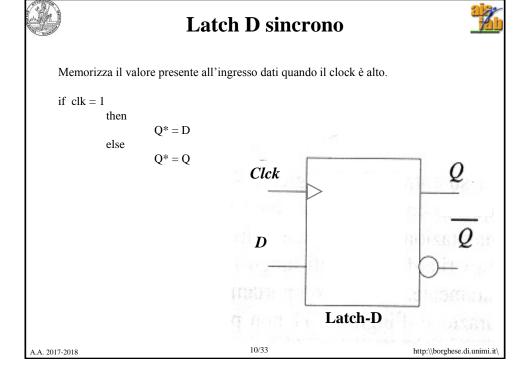

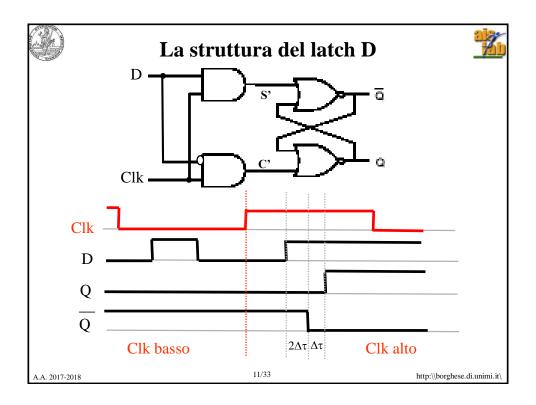

Latch sincroni D

Flip-flop

| AVDIO PO       |   |   |   |   |    |  |  |

|----------------|---|---|---|---|----|--|--|

|                | T | Q | S | C | Q* |  |  |

| Statist        | 0 | 0 | 0 | 0 | 0  |  |  |

| •              | 0 | 0 | 0 | 1 | 0  |  |  |

| •              | 0 | 0 | 1 | 0 | 0  |  |  |

| •              | 0 | 0 | 1 | 1 | 0  |  |  |

| •              | 0 | 1 | 0 | 0 | 1  |  |  |

| •              | 0 | 1 | 0 | 1 | 1  |  |  |

| •              | 0 | 1 | 1 | 0 | 1  |  |  |

| •              | 0 | 1 | 1 | 1 | 1  |  |  |

| •              | 1 | 0 | 0 | 0 | 0  |  |  |

| •              | 1 | 0 | 0 | 1 | 0  |  |  |

| •              | 1 | 0 | 1 | 0 | 1  |  |  |

| •              | 1 | 0 | 1 | 1 | X  |  |  |

| •              | 1 | 1 | 0 | 0 | 1  |  |  |

|                | 1 | 1 | 0 | 1 | 0  |  |  |

| •              | 1 | 1 | 1 | 0 | 1  |  |  |

| •              | 1 | 1 | 1 | 1 | X  |  |  |

| A.A. 2017-2018 |   |   |   |   |    |  |  |

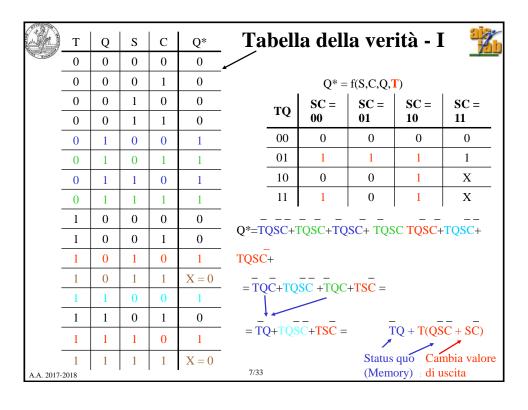

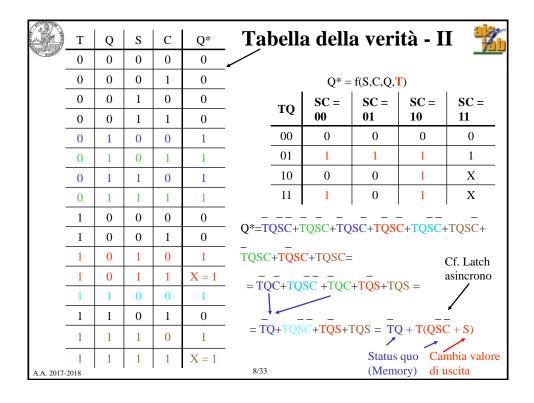

# Tabella della verità e 🌋 tabella di transizione

| TQ                          | SC = 00 | SC = 01 | SC =<br>10 | SC =<br>11       |  |  |  |

|-----------------------------|---------|---------|------------|------------------|--|--|--|

| 00                          | 0       | 0       | 0          | 0                |  |  |  |

| 01                          | 1       | 1       | 1          | 1                |  |  |  |

| 10                          | 0       | 10      | 1          | X                |  |  |  |

| 11                          | 1       | 0       | 1          | X                |  |  |  |

| $Q^* = f(S,C,Q,\mathbf{T})$ |         |         |            |                  |  |  |  |

| 5/33                        |         |         | hti        | :p:\\borghese.di |  |  |  |

### Tabella delle transizioni

http:\\borghese.di.unimi.it\

$$Q^* = f(S,C,Q,\mathbf{T})$$

| TQ | SC = 00 | SC = 01 | SC = 10 | SC = 11 |

|----|---------|---------|---------|---------|

| 00 | 0       | 0       | 0       | 0       |

| 01 | 1       | 1       | 1       | 1       |

| 10 | 0       | 0       | 1       | X       |

| 11 | 1       | 0       | 1       | X       |

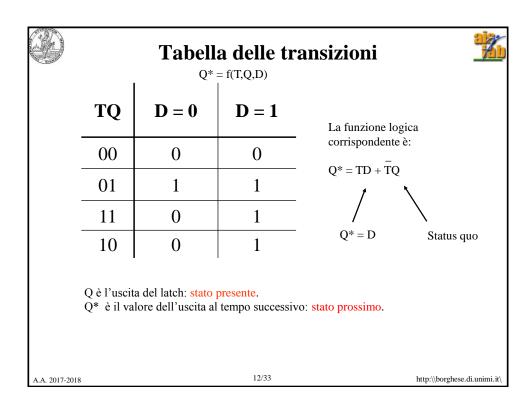

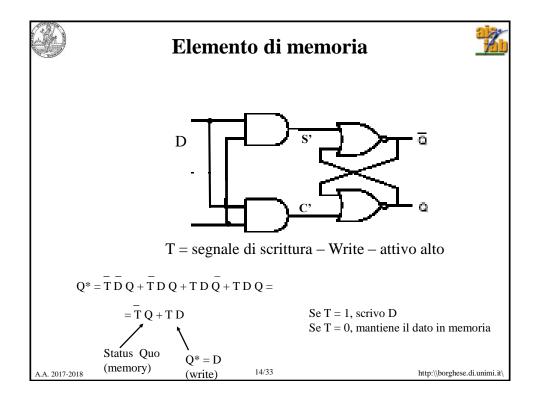

Q è l'uscita del latch: stato presente.

Q\* è il valore dell'uscita al tempo successivo: stato prossimo.

A.A. 2017-2018

6/33

### Sommario

http:\\borghese.di.unimi.it\

Latch sincroni SR

Latch sincroni D

Flip-flop

A.A. 2017-2018 9/33

### Sommario

Latch sincroni SR

Latch sincroni D

Flip-flop

A.A. 2017-2018 15/33

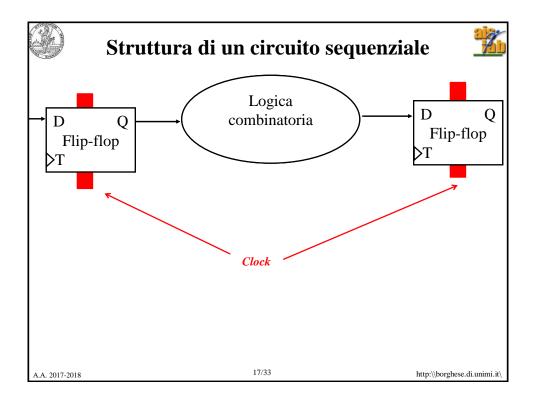

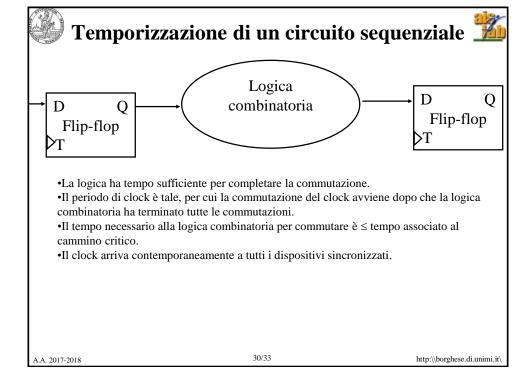

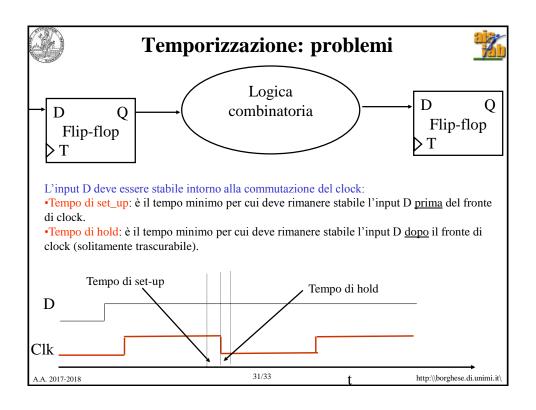

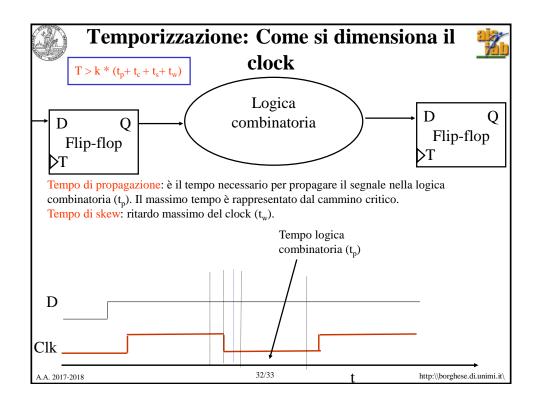

### I bistabili

http:\\borghese.di.unimi.it\

- Elementi di memoria (latch)

- "Cancelli" (flip-flop)

A.A. 2017-2018 16/33

http:\\borghese.di.unimi.it\

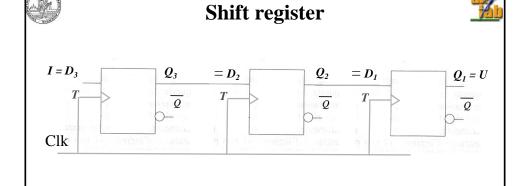

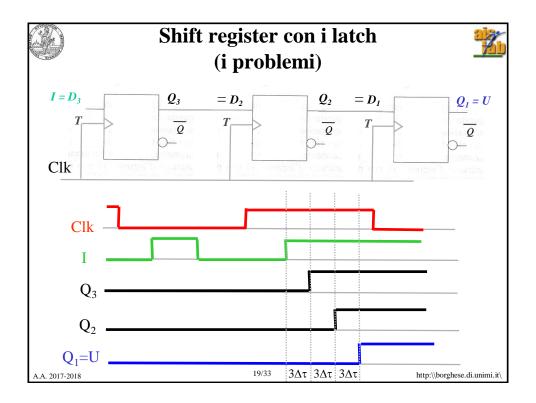

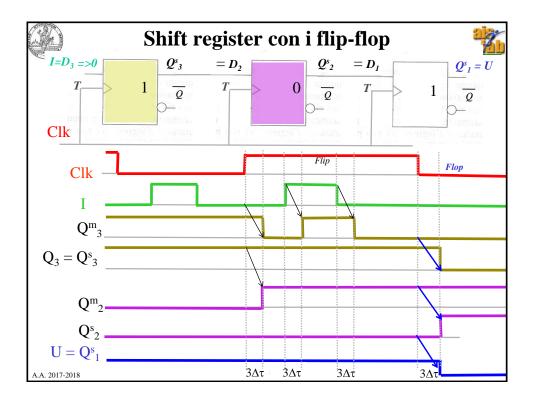

#### Registro a scorrimento (shift register o barrel shifter).

- •Un unico ingresso I e un'unica uscita U.

- •In presenza di un segnale attivo (clock alto), il contenuto viene spostato verso dx di una posizione.

- •Il valore contenuto nell'elemento più a dx dove va?

- •Qual'è il problema con l'utilizzo dei latch sincroni?

A.A. 2017-2018 18/33 http://borghese.di.unimi.it/

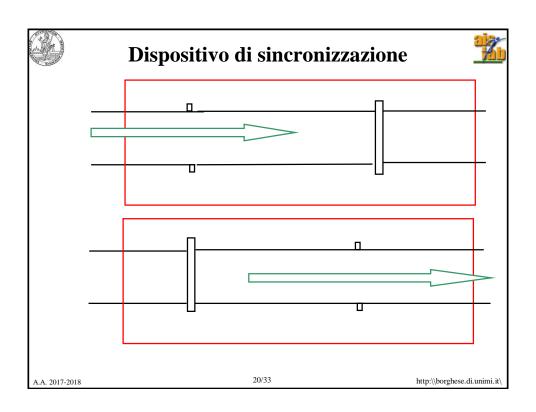

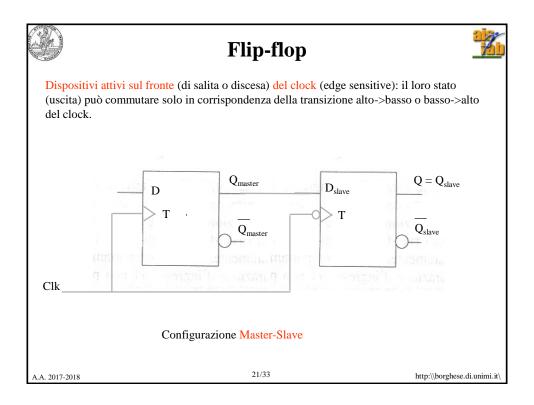

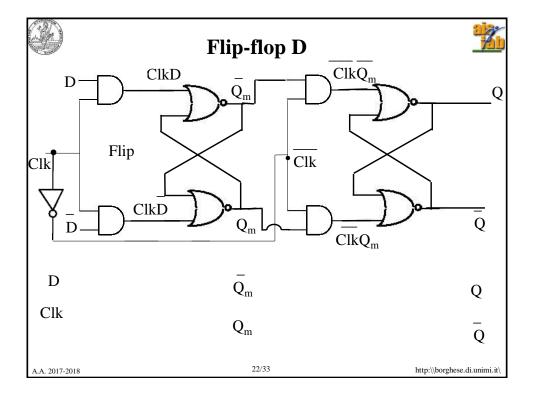

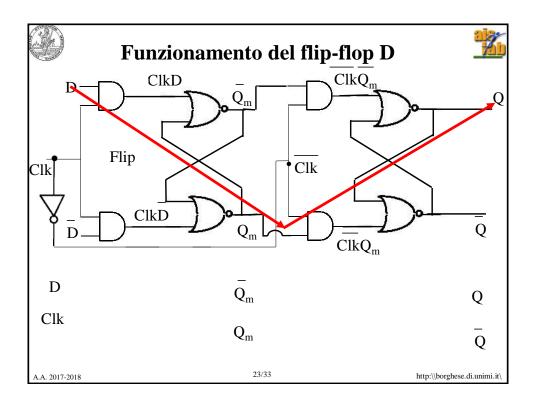

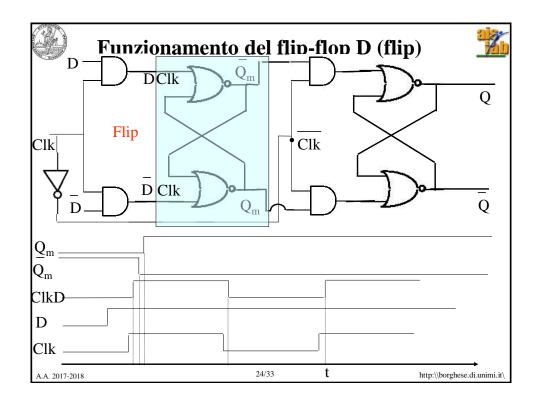

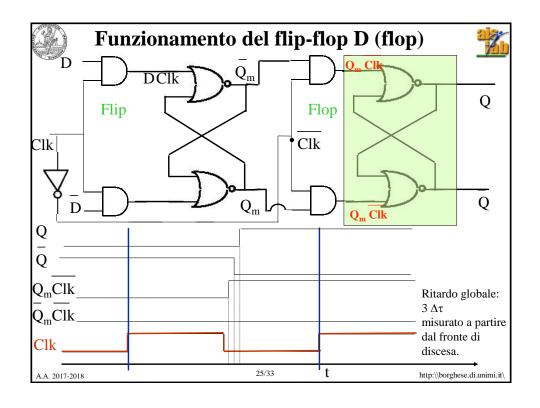

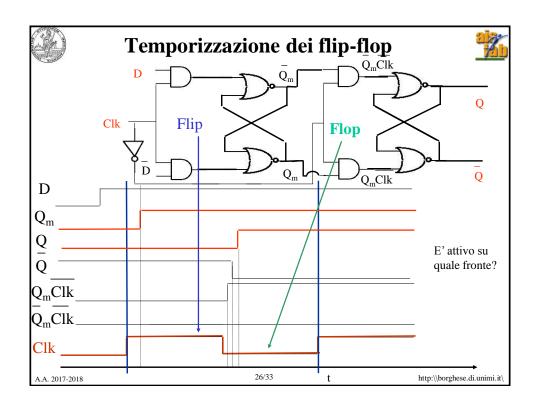

### **Configurazione master-slave**

- Semi-periodo di clock alto:

- Il master è trasparente: ingresso -> uscita del latch master.

- − Lo slave è "opaco" -> mantiene l'uscita.

- Lo slave è "disaccoppiato" dal latch master.

- Semi-periodo di clock basso:

- Il master è opaco: l'uscita del latch master si mantiene.

- Il master è "disaccoppiato" dall'ingresso esterno.

- Lo slave è trasparente e porta in uscita l'uscita del latch master.

A.A. 2017-2018 28/33

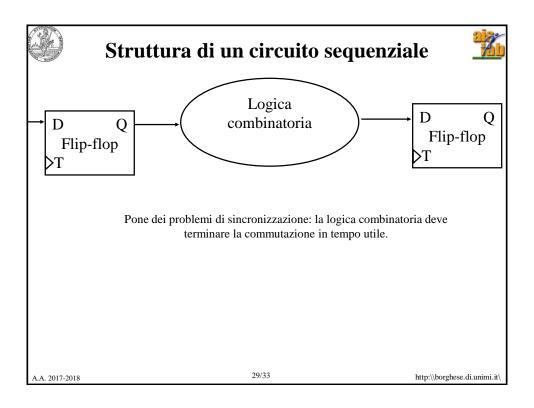

# Sommario

Latch sincroni SR

Latch sincroni D

Flip-flop

A.A. 2017-2018 33/33