## Circuiti sequenziali e latch

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

borghese@di.unimi.it

Università degli Studi di Milano

Riferimento Patterson: sezioni C.7 & C.8.

A.A. 2012-2013 1/32 http://borghese.di.unimi.it/

### Sommario

http:\\borghese.di.unimi.it\

Circuiti sequenziali

Latch asincroni

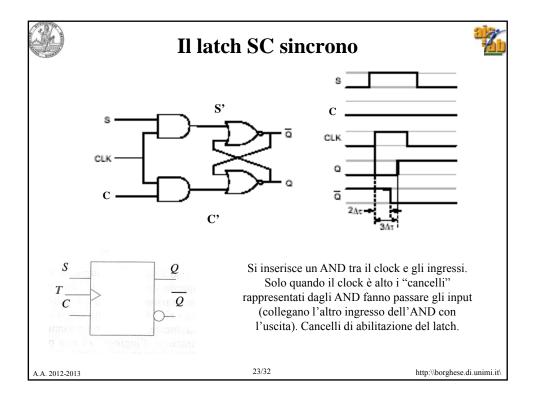

Latch sincroni SR

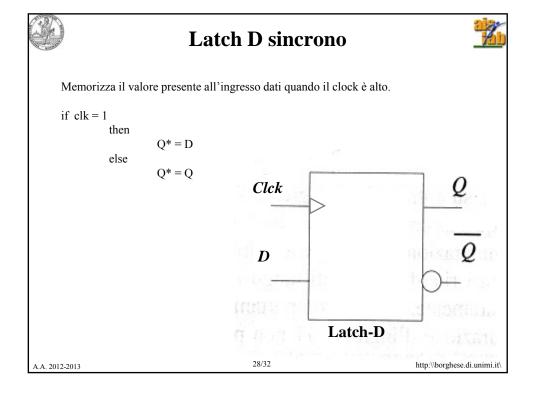

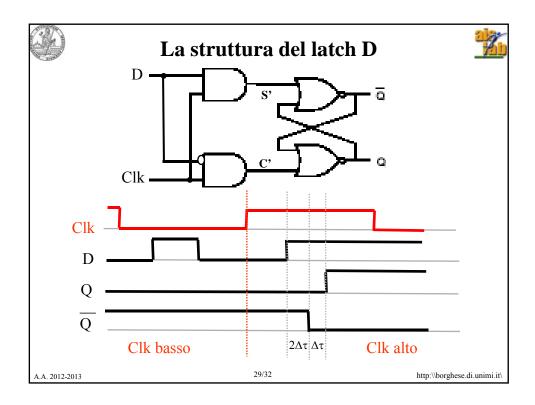

Latch sincroni D

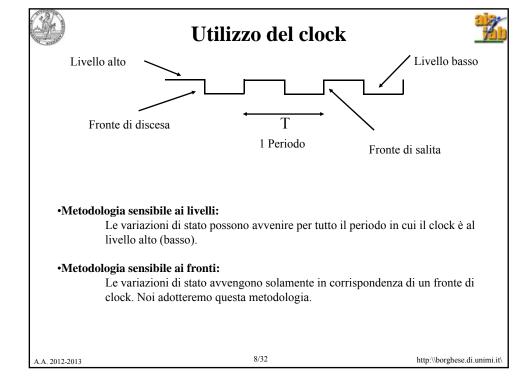

### Perchè esiste il clock?

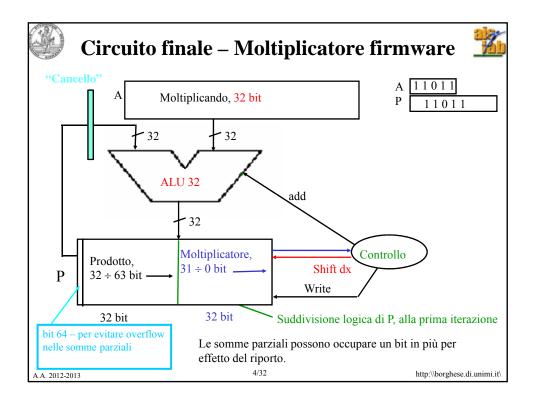

#### Esempio:

C = A + B

E = D + C

Quando posso calcolare E con lo stesso sommatore?

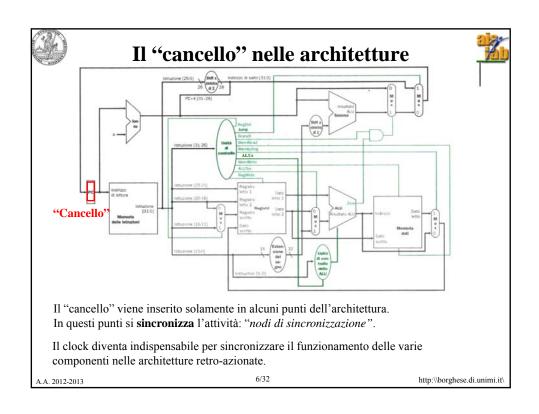

"Cancello" davanti all'ingresso del sommatore prima della seconda somma.

Ogni quanto tempo possiamo presentare gli ingressi al sommatore?

Dobbiamo essere ragionevolmente sicuri che il risultato sia stato calcolato ed utilizzato.

Occore una sincronizzazione dell'attività del sommatore.

A.A. 2012-2013 3/32 http://borghese.di.unimi.it/

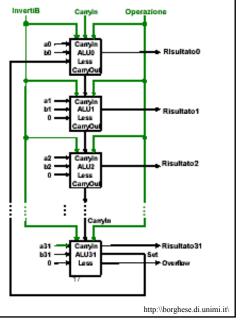

### Circuiti asincroni

- Architettura logica asincrona:

- L'elaborazione e propagazione dei segnali avviene in modo incontrollato, secondo le velocità di propagazione dei circuiti.

- Non devo mai aspettare il "tick" di un clock → massima velocità

- Progetto asincrono: Devo progettare il circuito in modo che nessun transitorio/cammino critico causi problemi → analisi di tutti i transitori critici possibili.

<u>Improponibile per circuiti con</u> feed-back.

Esempio: ALU.

A.A. 2012-2013

11/32

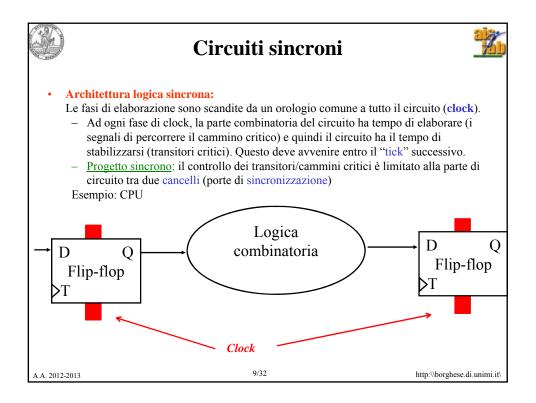

### Architetture sequenziali

- •I circuiti combinatori non hanno memoria. Gli output al tempo t dipendono unicamente dagli input al tempo t che provengono dall'esterno:  $\mathbf{y}^{t+1} = \mathbf{f}(\mathbf{u}^{t+1})$

- Sono necessari circuiti con memoria, per consentire comportamenti diversi a seconda della situazione dell'architettura. Nella memoria viene memorizzato lo **stato** del sistema che riassume la storia passata e la sequenza delle situazioni precedenti.

- I circuiti che hanno elementi di memoria consentono di eseguire operazioni sequenzialmente (scandite dal clock (e.g. CPU) o meno (e.g. Distributore di bibite)).

### Sommario

Circuiti sequenziali

Latch asincroni

Latch sincroni SR

Latch sincroni D

A.A. 2012-2013 13/32

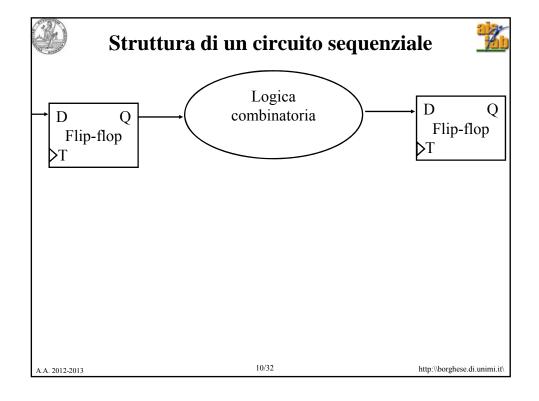

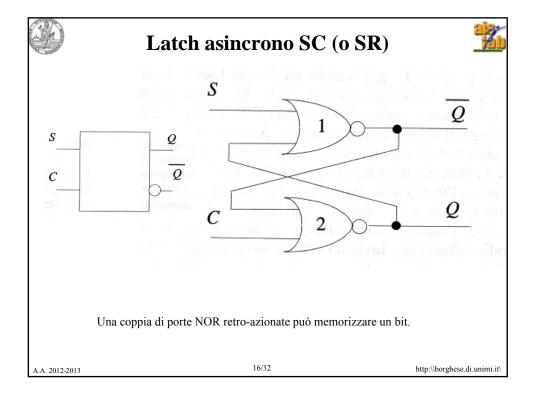

## Bistabili: latch e flip-flop

http:\\borghese.di.unimi.it\

Elemento cardine dei circuiti sequenziali è lo **stato.** Lo stato riassume il funzionamento negli istanti precedenti e deve essere immagazzinato (memorizzato).

Necessità di elementi con memoria (bistabili -> registri -> memorie).

Elemento base della memoria è il bistabile: dispositivo in grado di mantenere *indefinitamente* un certo valore di output (0 o 1).

Il suo valore di uscita coincide con lo stato. L'uscita al tempo t, dipende dallo stato (uscita) al tempo t-1 e dal valore presente agli input.

#### Tipi di bistabili:

- •Bistabili non temporizzati (asincroni) / temporizzati (sincroni).

- •Bistabili sincroni che commutano sul livello del clock (latch) o sul fronte (flip-flop).

A.A. 2012-2013 14/32 http:\\borghese.di.unimi.it\

A.A. 2012-2013

$http: \label{lem:http:/borghese.di.unimi.it} \\$

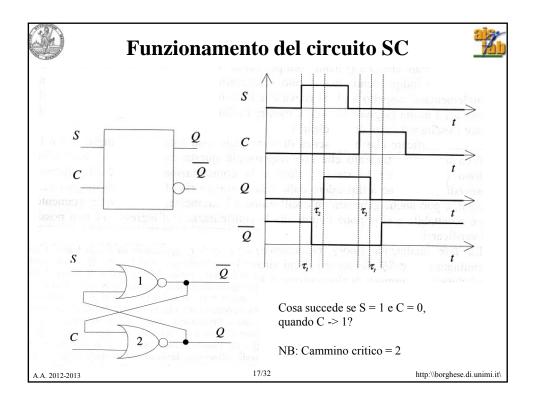

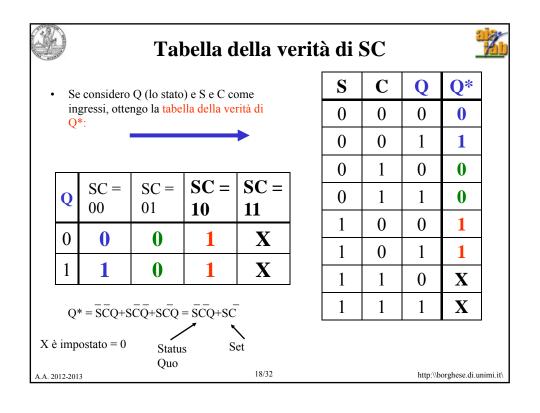

### Tabella delle transizioni

| Q | SC = 00 | SC = 01 | SC = 10 | SC =<br>11 |

|---|---------|---------|---------|------------|

| 0 | 0       | 0       | 1       | X          |

| 1 | 1       | 0       | 1       | X          |

|   | No      | Clear   | G.4     | l          |

No Clear change Reset (Q\* = Q) Write 0

Memory

Q è l'uscita del latch: stato presente, Q<sub>t</sub>

$Q^*$  è il valore dell'uscita al tempo successivo: stato prossimo,  $Q_{t+1}$

A.A. 2012-2013

19/3

### Tabella della verità di SC - II

Impostando X = 1 1, si ottiene:

$$Q* = \overline{SCQ} + S$$

(per assorbimento):

$$= \overline{CQ} + S$$

Status quo

$$SC = 11 -> Q* = 1 -> Set$$

Impostando X = 0.1, si ottiene:

$$Q^* = \bar{S} \bar{C} Q + \bar{S} \bar{C} + \bar{S} \bar{C} Q =$$

$$\overline{S \bigoplus C} \ Q + S \ \overline{C}$$

Status quo

$$SC = 11 -> Q* = 0 -> Reset$$

| S | C | Q | Q* |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 0 | 0 | 1 | 1  |

| 0 | 1 | 0 | 0  |

| 0 | 1 | 1 | 0  |

| 1 | 0 | 0 | 1  |

| 1 | 0 | 1 | 1  |

| 1 | 1 | 0 | X  |

| 1 | 1 | 1 | X  |

50 II Q 0 II**0**5

A.A. 2012-2013

http:\\borghese.di.unimi.it\

## Tabella delle eccitazioni

| Q | Q* | S | C |

|---|----|---|---|

| 0 | 0  | 0 | X |

| 0 | 1  | 1 | 0 |

| 1 | 0  | 0 | 1 |

| 1 | 1  | X | 0 |

Data la transizione Q -> Q\*, qual'è la coppia di valori di ingresso che la determina?

$(Q, Q^*)=f(S, C)$

A.A. 2012-2013

21/32

http:\\borghese.di.unimi.it\

### Sommario

Circuiti sequenziali

Latch asincroni

Latch sincroni SR

Latch sincroni D

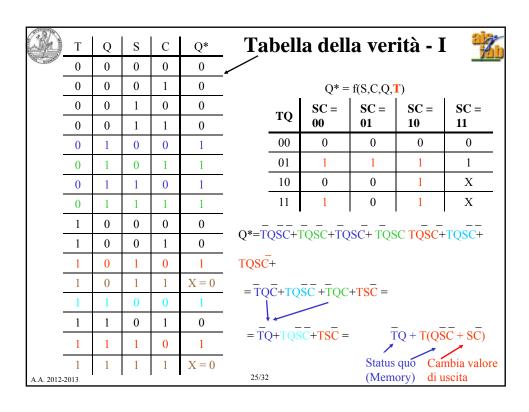

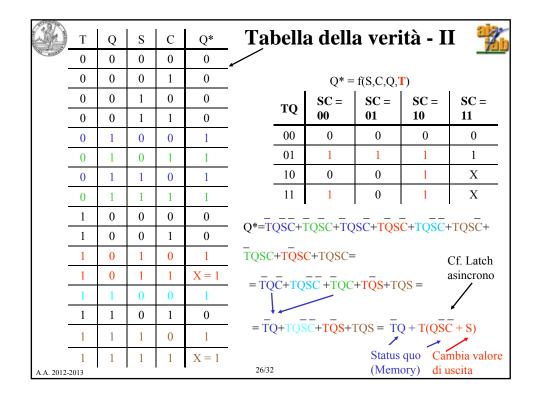

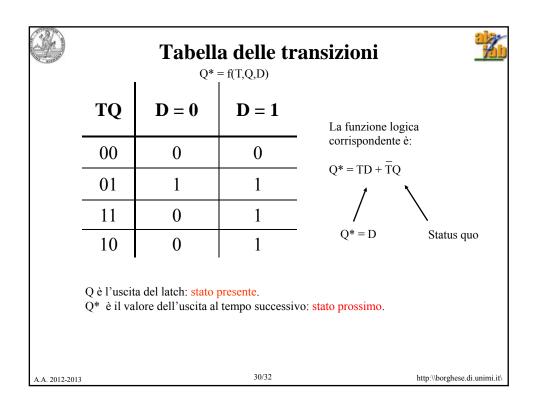

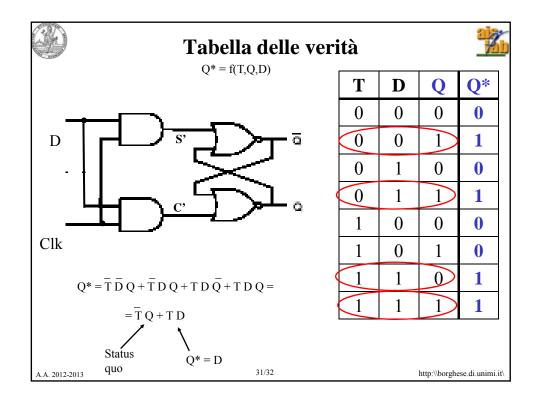

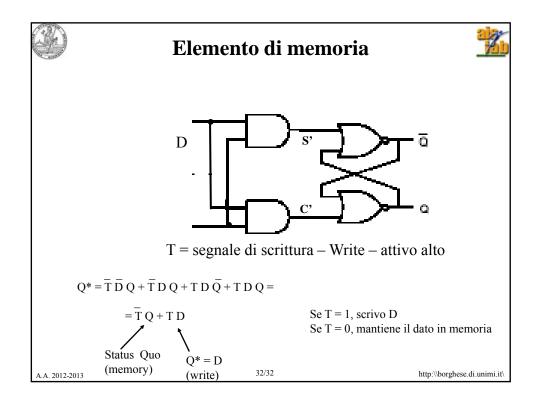

### Tabella delle transizioni

$$Q^* = f(S,C,Q,\mathbf{T})$$

| TQ | SC = 00 | SC = 01 | SC = 10 | SC = 11 |

|----|---------|---------|---------|---------|

| 00 | 0       | 0       | 0       | 0       |

| 01 | 1       | 1       | 1       | 1       |

| 10 | 0       | 0       | 1       | X       |

| 11 | 1       | 0       | 1       | X       |

Q è l'uscita del latch: stato presente.

Q\* è il valore dell'uscita al tempo successivo: stato prossimo.

## Sommario

Circuiti sequenziali

Latch asincroni

Latch sincroni SR

Latch sincroni D

A.A. 2012-2013

27/32

http:\\borghese.di.unimi.it\

# Sommario

$http: \label{lem:http://borghese.di.unimi.it} \\$

Circuiti sequenziali

Latch asincroni

Latch sincroni SR

Latch sincroni D

A.A. 2012-2013 33/32